嵌入式系统基础之:ARM处理器硬件开发平台

ARM11系列 | •ARM1136JF-S:使用ARMV6体系结构,性能强大(8级流水线,有静态/动态分支预测器和返回堆栈),有低延迟中断模式,有MMU,有支持物理标记的4-64k指令和数据cache,有一些内嵌的可配置的TCM,有4个主存端口(64位存储器接口),可以集成VFP协处理器(可选)。 •ARM1156T2(F)-S:有MPU,支持Thumb2ISA。 •ARM1176JZ(F)-S:在ARM1136JF-S基础上实现了TrustZone技术。 |

Cortex系列 | •Cortex-A8:使用v7A体系结构,支持MMU、AXI、VFP和NEON。 •Cortex-R4:使用v7R体系结构,支持MPU(可选)、AXI和DualIssue技术。 •Cortex-M3:使用v7M体系结构,支持MPU(可选)、AHBLite和APB |

因为本书所采用的FS2410开发板的S3C2410X是一款ARM9核处理器,所以下面重点学习ARM9核处理器。

2.ARM9主要特点

ARM处理器凭借它的低功耗、高性能等特点,被广泛应用于个人通信等嵌入式领域,而ARM7也曾在中低端手持设备中占据了一席之地。然而,ARM7的处理性能逐渐无法满足人们日益增长的高性能处理的需求,它开始退出主流应用领域,取而代之的是性能更加强大的ARM9系列处理器。

新一代的ARM9处理器,通过全新的设计,能够达到两倍以上于ARM7处理器的处理能力。它的主要特点如下所述。

(1)5级流水线。

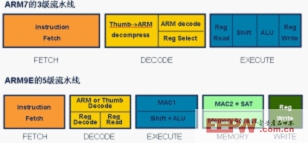

ARM7处理器采用的3级流水线设计,而ARM9则采用5级流水线设计,如图4.4所示。

通过使用5级流水线机制,在每一个时钟周期内可以同时执行5条指令。这样就大大提高了处理性能。在同样的加工工艺下,ARM9处理器的时钟频率是ARM7的1.8~2.2倍。

图4.4ARM7与ARM9流水线比较

(2)采用哈佛结构。

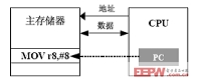

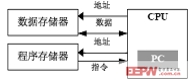

首先读者需要了解什么叫哈佛结构。在计算机中,根据计算机的存储器结构及其总线连接形式,计算机系统可以被分为冯·诺依曼结构和哈佛结构,其中冯·诺依曼结构共用数据存储空间和程序存储空间,它们共享存储器总线,这也是以往设计时常用的方式;而哈佛结构则具有分离的数据和程序空间及分离的访问总线。所以哈佛结构在指令执行时,取址和取数可以并行,因此具有更高的执行效率。ARM9采用的就是哈佛结构,而ARM7采用的则是冯·诺依曼结构。如图4.5和图4.6分别体现了冯·诺依曼结构和哈佛结构的数据存储方式。

图4.5冯·诺依曼结构 图4.6哈佛结构

由于在RISC架构的处理器中,程序中大约有30%的指令是Load-Store指令,而采用哈佛结构大大提升了这两个指令的执行速度,因此对提高系统效率的贡献是非常明显的。

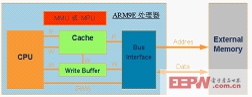

(3)高速缓存和写缓存的引入。

由于在处理器中,一般处理器速度远远高于存储器访问速度,那么,如果存储器访问成为系统性能的瓶颈,则处理器再快都毫无作用。在这种情况下,高速缓存(Cache)和写缓存(WriteBuffer)可以很好地解决这个问题,它们存储了最近常用的代码和数据,以供CPU快速存储,如图4.7所示。

(4)支持MMU。

图4.7ARM9的高速缓存和读缓存

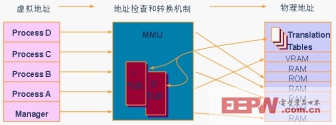

MMU是内存管理单元,它把内存以“页(page)”为单位来进行处理。一页内存是指一个具有一定大小的连续的内存块,通常为4096B或8192B。操作系统为每个正在运行的程序建立并维护一张被称为进程内存映射(ProcessMemoryMap)的表,表中记录了程序可以存取的所有内存页以及它们的实际位置。

每当程序存取一块内存时,它会把相应的虚拟地址(virtualaddress)传送给MMU,而MMU会在PMM中查找这块内存的实际位置,也就是物理地址(physicaladdress),物理地址可以在内存中或磁盘上的任何位置。如果程序要存取的位置在磁盘上,就必须把包含该地址的页从磁盘上读到内存中,并且必须更新PMM以反映这个变化(这被称为pagefault,即“页错”)。MMU的实现过程如图4.8所示。

图4.8MMU的实现过程

只有拥有了MMU才能真正实现内存保护。例如当A进程的程序试图直接访问属于B进程的虚拟地址中的数据,那么MMU会产生一个异常(Exception)来阻止A的越界操作。这样,通过内存保护,一个进程的失败并不会影响其他进程的运行,从而增强了系统的稳定性,如图4.9所示。ARM9也正是因为拥有了MMU,所以比ARM7具有更强的稳定性和可靠性。

图4.9内存保护示意图

4.2.4S3C2410处理器详解

本

ARM处理器 ARM9 嵌入式系统 哈佛结构 S3C2410 相关文章:

- 关于对ARM处理器中“8位位图”的理解(12-01)

- ARM处理器工作模式(11-28)

- ARM处理器模式介绍和模式切换(11-28)

- ARM处理器的总线信号(11-27)

- 选择ARM处理器,ARM7还是Cortex-M3(11-27)

- GNU ARM汇编--(三)ARM处理器的基本原则(11-26)