基于大容量FPGA的多节点系统的远程升级的实现

个芯片内,ATmega64 成为一个功能强大的单片机,为许多嵌入式控制应用提供了灵活而低成本的解决方案。

利用ATmega64单片机实现对大容量FPGA的远程升级,涉及的主要技术问题有三点:一是如何将ATmega64单片机接入RS485总线;二是在接收到升级数据后和加载FPGA时,如何利用ATmega64单片机对大容量的Flash存储器进行读写操作;三是ATmega64单片机实现FPGA的SELECTMAP加载。

2.2.1 RS485接口电路设计

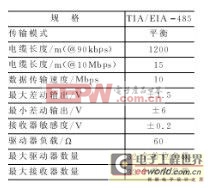

如表1所列, RS485总线标准具有控制方便、价格低廉以及高噪声抑制、相对高的传输速率、传输距离远和宽共模范围等优点。在过去的20年时间里,建议性标准RS485作为一种多点差分数据传输的电气规范,被应用在许多不同的领域作为数据传输链路。

表1 TIA/EIA485串行通信标准的性能

子节点的ATmega64单片机通过Sipex公司设计生产的高性能RS485收发器接入RS485总线。

SP485R是一款与流行的标准RS485芯片完全兼容,而且包含更高的ESD保护和高接收器输入阻抗等性能的RS485收发器。接收器输入高阻抗可以使400个收发器接到同一条传输线上,又不会引起RS485驱动器信号的衰减。该收发器的特点如下:

① 允许超过400个收发器接到同一条传输线上;

② 接收器输入高阻抗(标准值RIN=150 kΩ);

③ 半双工配置与工业标准引脚一致;

④ 共模输入电压范围为-7~+12 V;

⑤ 低功耗(250 mW);

⑥ 独立驱动器和接收器使能引脚。

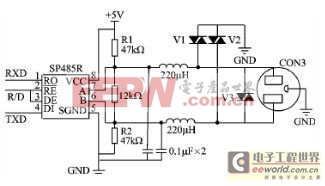

其典型应用电路如图3所示。

图3 利用SP485R构成的半双工RS485电路

ATmega64单片机的标准串行口通过RXD直接连接SP485R芯片的RO引脚,通过TXD直接连接SP485R芯片的DI引脚。由单片机输出的R/D信号直接控制SP485R芯片的发送器/接收器使能:R/D信号为1,SP485R芯片的发送器有效,接收器禁止,此时单片机可以向RS485总线发送数据字节;R/D信号为0,SP485R芯片的发送器禁止,接收器有效,单片机可以接收来自RS485总线的数据字节。上拉电阻R1、下拉电阻R2用于保证未连接总线时的SP485R芯片处于空闲状态,以提高每个RS485节点的工作可靠性。6.8 V的TVS管V1、V2、V3用来保护RS485总线,避免RS485总线受外界干扰时产生的高压损坏RS485收发器。

2.2.2 ATmega64存储空间的扩展

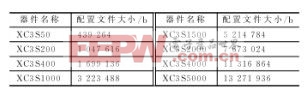

ATmega64的寻址空间为64 KB,利用ATmega64自身的寻址系统,只能访问0x0000~0xFFFF的地址空间。显然,这对于存储和加载大容量FPGA的配置数据是远远不够的。以Xilinx公司的Spartan3系列FPGA为例,其配置数据所需的存储空间如表2所列。

表2 Spartan3系列FPGA配置文件大小

以XC3S4000型FPGA为例,它的配置文件所需的存储空间约为1.35 MB,已远远超出了ATmega64单片机的寻址空间。因此,为了能够利用ATmega64单片机来实现对FPGA配置数据的读写,必须对其寻址空间进行扩展。扩展的硬件连接框图如图2中的单片机与Flash的连接部分所示。

本设计中是使用通用I/O来扩展ATmega64单片机的寻址空间的。ATmega64单片机的总寻址空间为64 KB,但片内4 KB的SRAM及各种寄存器占用了前面的部分寻址空间,故其片外存储器寻址空间是0x1100~0xFFFF。因此将Flash的低15位地址直接接到ATmega64单片机的低15位地址总线上,其余6位高位地址用单片机的通用I/O进行选择。寻址时单片机的专用地址口只输出0x8000~0xFFFF的地址数据,与通用I/O输出的地址组合后给出Flash的读写地址。

通过以上对ATmega64单片机寻址空间的扩展方法,可以实现ATmega64单片机对合适的Flash存储器的寻址操作,从而解决了大容量FPGA配置数据的存储和读取问题。

2.2.3 用ATmega64实现FPGA的SELECTMAP加载

Xilinx公司的Spartan3系列FPGA加载方式分为5种: Master Serial、Slave Serial、Master Parallel、Slave Parallel、JTAG。

按照FPGA是否控制加载过程,加载方式可分为Master方式和Slave方式;按照加载数据时的数据位宽,可分为Serial方式和Parallel方式。用于加载的引脚主要有: PROG_B,CCLK,RDWR_B,DONE,INIT_B,CS_B,BUSY,D[0~7],M[0~2],HSWAP和JTAG接口(TDI、TMS、TCK、TDO)。加载过程大体分为3个步骤:配置的建立、配置数据的加载和加载完成。

SELECTMAP即Slave Parallel方式,是由外部控制器控制FPGA的加载过程,并以8位数据的形式向FPGA写入加载数据的加载方法。图2中FPGA与ATmega64的连接部分为ATmega64单片机采用SELECTMAP方式对FPGA进行加载的硬件连接框图,具体实现过程如下:

ATmega64通过将FPGA的PROG_B、CS_B和RDWR_B引脚置低来开启加载过程,FPGA在PROG_B置低后开始清除内部配置RAM,并将INIT_B脚置低。PROG_B重新置1后,在INIT_B由低变高的上升沿,FPGA采

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)