使用先进技术来加速SoC验证

摘要:近年来,由于设计复杂度的增长,对于验证提出了更高的要求。验证环境变得越来越大,越来越复杂,设计和验证的双重压力导致仿真变得越来越慢。所有验证/仿真的速度已经成为当前SOC设计进程中的重大挑战。

在我们的项目中,我们使用Synopsys的验证flow以及近年来Synopsys提供的新的方法/工具,比如性能分析工具来分析仿真瓶颈,使用分块编译来加速编译,使用并行多核技术来加速编译/运行。使用UVM来增加环境的可复用性,等等,这些技术/特性的引入都大幅度加速了我们的仿真速度并减少了仿真时间。

项目以及验证环境介绍

我们的项目是GPU的项目,对于仿真性能有较高的要求,所以在项目中希望使用尽可能多的新技术来缩短仿真时间以及加速验证。

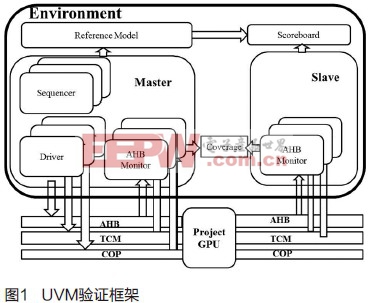

我们的验证环境使用UVM标准库来搭建的。验证环境如图1所示。

使用了Synopsys公司的VCS来作为我们的仿真工具。

工具版本:VCS 2012.09-SP1,Verdi 2013.04

硬件环境如表1所示。

加速编译的方法

随着电路规模的不断变大,编译时间也成为了仿真过程中重要因素,如何加快/重用编译数据库,是加速整个仿真过程不可缺少的部分。VCS提供了很多好的技术来加速编译过程。

并行编译

当前基本上我们的服务器都能提供多核支持,并行编译选项可以使用服务器的多核来提供更快的并行处理,来快速编译生成数据库。VCS并行编译的选项如下:

-j[no_of_processes]

比如 vcs –j4 …,注意no_of_processes的数目不要超过实际可以提供的物理核数目。

增量编译

在编译过程中,VCS会创建设计/验证的层次结构,当你重新编译的时候,VCS只会就那些更改的设计单元进行重新编译,这样可以缩短编译时间。现在增量编译选项已经成为VCS的默认选项。

分区编译 (Partition Compile)

分区编译是VCS提供的一个比较新的特性。这个特性可以让我们把设计/验证中的实例/模块分成不同的大得区块来编译。这样如果之后只对其中一部分区块相关的文件进行了修改,那么可以重用之前分区编译的数据库来减少其它区块编译的时间,只对修改的区块进行重新编译即可。同时针对验证环境中的package,比如像UVM标准库或者一些算法库,分区编译也可以提前把它们分块编译好,然后这样可以加速验证环境的编译速度。

运行性能的提升的方法

在仿真过程中,运行的时间以及内存消耗是单次仿真的主要瓶颈,因此本文会关注在运行过程中如何提升性能,包括如何找到运行过程的瓶颈以及使用多核技术来加速仿真。

运行性能分析工具

VCS提供了用于分析性能的Profile工具Simprofile,使用在仿真过程中生成时间/内存消耗的报告,然后可以通过对于报告的分析来找到限制当前仿真性能的瓶颈。使用方式:

编译:%VCS –simprofile –lca –f filelist.f …

运行:%simv –simprofile time|mem

一般在运行后会自动生成名为simprofile_dir的报告目录,也可以后处理生成报告:

%profrpt –output_dir simprofile_dir –view time_all|mem_all

Simprofile会默认生成基于HTML的报告,然后可以进行选择查看相关的性能选项(支持模块/功能/DPI/PLI/约束/覆盖率等),同时支持对多次仿真的报告进行比较。

多核仿真技术

VCS提供了多核仿真技术用于使用服务器的物理多核来加速仿真。使用多核技术可以把一次仿真的不同部分分配到多个物理运算单元上以达到加速仿真的目的。现在提供了两种多核模式:应用级并行技术(ALP)和设计级并行技术(DLP),ALP/DLP以及二者的组合通过多核CPU来优化仿真进程。

应用级多核技术(ALP)

应用级多核技术(ALP)是把按照应用把验证的不同部分(Testbench、SystemVerilog断言、覆盖率统计、波形保存等等)放到多个处理核上去做并行运行。

例如:在一个4核服务器上我们可以把覆盖率统计放到第一个核上,把断言检测放到第二个核上,把波形保存放到第三个核上,剩下的仿真放到最后一个核上。结果会看到仿真性能可以得到很大提升。表1是ALP支持的开关参数以及推荐的使用示例

如果VCS使用了ALP+fsdb多核(+mtfsdb),那么会在控制台看到如下打印:

*Novas* : Multi-Thread VCS dumping is enabled

同时Verdi3自动支持对FSDB进行并行保存,如果使能了并行保存,那么会有如下信息:

*Novas* : Enable parallel dumping

设计级多核技术(DLP)

DLP允许我们可以把一个大的设计分成多个区块,然后把不同的区块放入不同的计算核去运行。DLP的一般会根据profiler的报告结果以及设计部件之间的相关性分析来做划分。把划分写

SoC Synopsys GPU VCS 仿真 201312 相关文章:

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)