低功耗8-bit 200MSPS时间交织流水线ADC

摘要:本文介绍了一款低功耗8位200MSPS的模数转换器。ADC是由时间交织和逐级递减技术来实现低功耗的。流水级和放大器的设计保证了低电流下满足工艺、电压、温度(PVT)变化。本ADC采用0.35μm 双层多晶硅栅三层金属的CMOS工艺,在200MHz采样频率和41MHz输入信号频率下达到47.7dB的SNDR。在3V的电源电压下功耗仅为120mW,不包括输出缓冲器。

引言

移动无线通信系统是模拟数字转换器的主要应用。高性能的交流特性,主要包括信噪比(SNR)和无杂散动态范围(SFDR),能够提供更好的无线通信覆盖率,更多的载波,更好的质量和可靠性。功耗和面积对于移动无线通信系统也非常重要。

在多种ADC中,流水线ADC是最适合做高速高精度的。目前的设计趋势是在低功耗下实现高性能。运放共享及开关运放技术被广泛地应用于降低功耗上[1-3]。但是此技术只适合低速ADC。本文中采取的一些技术可以在不牺牲性能的情况下来节省功耗。该ADC在200MSPS,输入信号频率为41MHz时达到47.7dB的信噪比,电流仅为40mA。

论文的组织如下:第二章介绍流水线ADC的结构。第三章介绍了流水级、放大器和基准产生电路等的具体结构。第四章给出最终的测试结果。

流水线ADC的结构

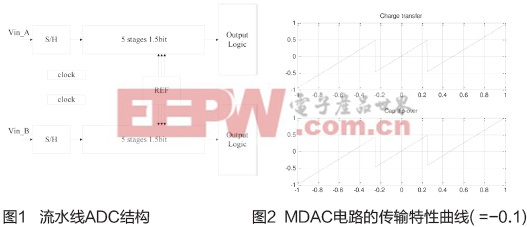

流水线ADC有两个通道,每个通道都工作在100MHz下,包括5个1.5 bit流水级和一个3bit flash ADC。传统的转换器。第一级流水级一般为多位数,例如3.5bit或4.5bit。但在文中采用的是1.5bit的。其中有两个原因:第一,文中ADC是时间交织的。它有两个通道,任何不匹配都会降低性能。第一级的多位数会引起比1.5bit更多的失配,因为多位数相对于1.5位会有更多的电容和开关。第二,在8位100MHz ADC中放大器功耗不大,所以第一级选取多位数并不比采用1.5bit和逐级递减技术的更省功耗。系统结构如图1所示。

流水线ADC中还有基准源和时钟等。基准源必须满足PVT变化,所以要仔细设计符合要求;时钟发生器为所有流水级提供时钟,时钟偏移会严重影响性能。时钟的驱动必须设计适当,如果驱动太大会消耗过多的功耗,而版图中会有很多寄生电容,所以为保证性能要留一些裕度。

电路实现

流水级

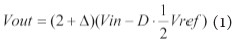

流水级有三种结构:开环,闭环电荷转移,闭环电容翻转[4]。开环结构可以降低对放大器的要求,但是由于严重的非线性必须要有后台或者前台的数字校正电路。在8位100MSPS流水线ADC中,放大器的设计并不是瓶颈,所以并不选择开环结构。两种闭环结构在理想情况下有相同的功能,但他们在有电容失配的情况下则表现不同。电荷转移结构的传输函数如下[5](Cs/Cf=1不考虑其它的非理性因素):

Vin是输入信号, 是电容失调,D是数字输出,Vref 是基准电压,电容翻转结构的传输函数如下:

图2为两种结构在电容失配10%时的传输特性曲线 (Δ=-0.1):

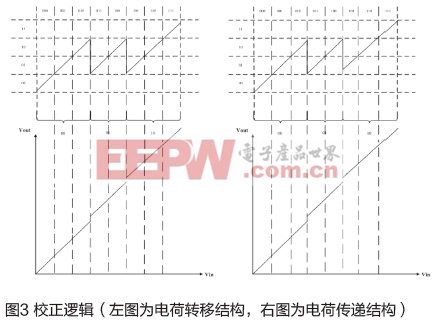

如图2所示,对于电荷转移结构来说,第一个和最后一个交叉点总是位于-1/2 和 1/2处,但输出幅度会被Δ影响。对于电容翻转式结构,第一个和最后一个交叉点会被Δ影响,但是输出幅度不会被Δ影响。在电荷转移结构的-1/4 和1/4处的跳变高度相对电容翻转式结构来说更接近Vref,分别为0.95Vref和0.9Vref。流水线ADC一般采用冗余位用来校正。如果失调只发生在第一级(假设其他级都是理想的且都是2bit),那么校正过程如图3所示。

因为交叉点总是都在-1/2 和1/2处,且1/4 或-1/4处的跳变高度比电容翻转式的大,电荷转移结构能更好的实现校正。

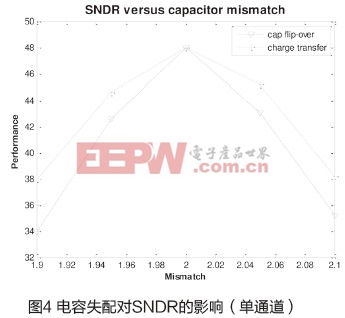

当Δ是正数时,电荷转移结构会造成失码,但是对比于电容翻转结构在交叉点和跳变电的偏差,失码引起的误差对性能造成的影响较小。图4给出不同电容失配情况下两种结构SNDR的变化。

电荷转移结构也有缺点,最重要的一点是较小的反馈因子造成对放大器更高的要求。但是在8位100MHz流水线ADC中,放大器并不是困难,所以消耗一些电流来减小电容失配对系统性能造成的影响是有必要的。

放大器

本电路采用的不是传统的两级放大器。第一级是共源放大器,第二级是共源共栅放大器,如图5所示。

跟跟传统二级放大器比有两个优点。第一,其增益要比传统结构的高。因为第二级放大器是共源共栅放大器,所以输出阻抗大,进而增益也大。第二,因为第二级是输出级,所以输出级的极点是主极点。通过仔细的设计,可以使主极点远离第一级的非主极点。这就意味着不需补偿,减小了负载电容,所以与传统放大器比,更小的电流可以获得更高的带宽。这对低功耗设计非常重要[6]。

这里选用了开关电容共模负反馈,因为它相对连续时间共模负反馈更稳定。这里有一个改动,即增加了SD1和SD2两个开关。

ADC 放大器 无线通信 流水线 时钟 201312 相关文章:

- 基于DSP的广播级数字音频延时器(06-07)

- 基于AD9268的短波接收全数字传输结构(07-25)

- DSP与数据转换器协同工作所必须考虑的10大因素(01-26)

- 基于ADC0809和51单片机的多路数据采集系统设计方案(10-29)

- 基于TLC320AC01与DSP的接口电路设计(01-15)

- 基于DSP和CPLD技术的多路ADC系统的设计方案(05-19)