FRAM使安全气囊系统更加智能化

时间:01-04

来源:互联网

点击:

汽车安全系统预期在未来几年变得更复杂。这一趋势的主要动力是预期规则将影响附加速率和安全气囊复杂性以及控制系统稳定性。这些系统的电子部分将会增加,用于这些系统的半导体存储器的需求也将增加。本文简要地研究在为较新型安全气囊选择存储器方案时应考虑的问题。

安全气囊系统正在经历两个主要变革。首先,在较新型的安全气囊系统中,增加了“智能”。不再像过去那样用最大力打开气囊,好像所有的事故和乘客状况都相同,而是根据具体的事故和乘客参数确定作用力,可能包括碰撞的严重度、乘员的重量以及座位相对安全气囊的位置。那些曾经受过标准安全气囊影响的人会对赞同可变力的。智能安全气囊也能分辨出乘客座位是否为空,如果为空,乘客安全气囊就不必要打开。考虑到每部汽车的安全气囊数量在增加,并且在即使很小的事故中更换气囊的成本也在增加,因此在为消费者大幅节省修理和保险成本方面,这一变革是有潜力的。

第二个变革是汽车正日益配置事件数据记录仪(EDR),这种装置能收集碰撞信息,类似于飞机的“黑匣子”。安全气囊电子控制单元(ECU)通常包括有EDR功能。这一分法很自然,因为EDR没有飞机“黑匣子”的残存性要求,并且安全气囊控制器是大量重要的传感器输入的主要接收者。汽车制造商也很快指出没有独立使用EDR的空间。

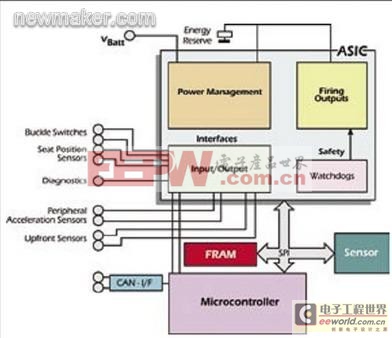

这两种安全气囊存储器应用对存储器的要求很苛刻,但两者却完全不同。因为在重事故中很可能电源会在某种程度上丧失,所以两者都需要一个非易失性存储器。要重建事件,则数据必须存储到系统中能写入的鲁棒的非易失性存储器中。图1给出了一种具有FRAM存储器存储的基本安全气囊系统的框图。

对EDR,难点与希望的数据量和可用的存储时间有关。预计新规则将大大扩展要获取的数据量。发生严重事故时,电源很可能丢失。这时,EDR系统在系统掉电前,快速将数据储存下来。在事故中,电源总是突然断掉,常规非易失性存储方案花费时间太长,无法编程新信息。

FRAM提供的技术方案能同时应对这两种挑战。像其它的可选方案一样,FRAM具有可靠的非易失性存储。主要差别是其写操作的高耐久性(能写很多次)和写速度。

安全气囊应用普遍选择5V工作的串行外设接口(SPI)FRAM存储器,这些器件的写耐久性超过1万亿次(1×1012)写操作,这足够智能安全气囊连续写操作了,能实现乘员数据无缝记录。这些器件也能以总线接口速度进行写操作。无延迟地以5MHz到20MHz速率写能使主处理器流数据尽可能地快,同时丢失信息的风险非常小。非易失性、无与伦比的写耐久性再配上快速数据采集能力,使FRAM成为下一代高级安全气囊系统的理想存储器工艺。

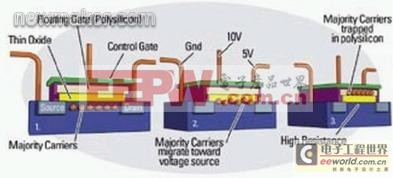

以前,汽车应用的主要非易失性存储器工艺是栅极悬空的器件,如EEPROM或闪存。栅极悬空器件都采用一SiO2薄层将多晶硅栅极与沟道隔离。对器件编程时,在控制栅极上产生高压使电子加速流向源极(N沟道器件)。因此,电子获得足够的动能穿透绝缘层,在多晶硅材料上被捕获(见图2)。

随着汽车设计要求复杂性的提高,栅极悬空存储器工艺的局限性越来越明显。例如,编程工艺要用几ms,对安全性很关键的应用这一时间太长了。对事故中出现的这种电源快速断电情况,栅极悬空器件能成功存储的信息几乎没有。

编程工艺对绝缘层也是破坏性的,因此,这类器件的写耐久性有限,通常为100,000~1,000,000个写操作。例如,在乘员传感器中,对这一上限值,其数据更新就太频繁了。假如写操作的典型要求是每秒1次,栅极悬空的器件工作不到12天就会毁坏。将数据缓冲到RAM中,再在掉电时写进栅极悬空的非易失性存储器会使EDR出现速度问题,不是一个真正的解决方案。

在智能安全气囊系统中,在碰撞事故中存储数据不仅必要,而且在事故前存储碰撞前的数据也很值得。使用轮询记录方法存储碰撞前数据最理想,但是对栅极悬空器件,这一方案证明是有问题的,原因是其耐久性有限。由于安全气囊模块用来储存能量以起爆安全气囊的电容很大,因此也会留有足够的剩余能量以在爆管起爆后从缓冲器写数据。能够写的数据量受可用能量的限制,就是说与电容器中残留能量和被写存储器的速度有关。典型的2K字节的栅极悬空存储器件写速度大约为4字节/5ms。因此,完整写栅极悬空存储器件要花1s以上的时间。

使用FRAM是一种方案,其FRAM的高耐久性和高速度能同时有效解决这两个问题。Ramtron的FRAM工艺将铁电材料和标准半导体芯片设计及制作工艺结合在一起,生产非易失性存储和模拟/混合信号产品。这些产品将高速读/写性能、几乎无限的写耐久性和静态RAM(SRAM)的低功耗,以及在电源丢失情况下标准RAM工艺所无法达到的安全存储数据的功能结合在一起。

FRAM电池采用工业标准的互补型金属氧化物半导体(CMOS)工艺制作,在两个电极板间的铁电晶体形成电容,类似于DRAM电容的结构。与易失性存储器给电容器充电来存储数据的方式不同,FRAM是将数据存储在铁电晶体内部。

给铁电晶体加上电场时,中心原子就向电场方向移动,随着原子移动到晶体内部,它穿过势垒,产生电荷尖峰信号。内部电路感测此电荷尖峰信号并复位存储器。如果将电场从晶体上移开,中心原子就呆在原位,保存存储器状态(见图3)。

安全气囊系统正在经历两个主要变革。首先,在较新型的安全气囊系统中,增加了“智能”。不再像过去那样用最大力打开气囊,好像所有的事故和乘客状况都相同,而是根据具体的事故和乘客参数确定作用力,可能包括碰撞的严重度、乘员的重量以及座位相对安全气囊的位置。那些曾经受过标准安全气囊影响的人会对赞同可变力的。智能安全气囊也能分辨出乘客座位是否为空,如果为空,乘客安全气囊就不必要打开。考虑到每部汽车的安全气囊数量在增加,并且在即使很小的事故中更换气囊的成本也在增加,因此在为消费者大幅节省修理和保险成本方面,这一变革是有潜力的。

第二个变革是汽车正日益配置事件数据记录仪(EDR),这种装置能收集碰撞信息,类似于飞机的“黑匣子”。安全气囊电子控制单元(ECU)通常包括有EDR功能。这一分法很自然,因为EDR没有飞机“黑匣子”的残存性要求,并且安全气囊控制器是大量重要的传感器输入的主要接收者。汽车制造商也很快指出没有独立使用EDR的空间。

这两种安全气囊存储器应用对存储器的要求很苛刻,但两者却完全不同。因为在重事故中很可能电源会在某种程度上丧失,所以两者都需要一个非易失性存储器。要重建事件,则数据必须存储到系统中能写入的鲁棒的非易失性存储器中。图1给出了一种具有FRAM存储器存储的基本安全气囊系统的框图。

对EDR,难点与希望的数据量和可用的存储时间有关。预计新规则将大大扩展要获取的数据量。发生严重事故时,电源很可能丢失。这时,EDR系统在系统掉电前,快速将数据储存下来。在事故中,电源总是突然断掉,常规非易失性存储方案花费时间太长,无法编程新信息。

FRAM提供的技术方案能同时应对这两种挑战。像其它的可选方案一样,FRAM具有可靠的非易失性存储。主要差别是其写操作的高耐久性(能写很多次)和写速度。

安全气囊应用普遍选择5V工作的串行外设接口(SPI)FRAM存储器,这些器件的写耐久性超过1万亿次(1×1012)写操作,这足够智能安全气囊连续写操作了,能实现乘员数据无缝记录。这些器件也能以总线接口速度进行写操作。无延迟地以5MHz到20MHz速率写能使主处理器流数据尽可能地快,同时丢失信息的风险非常小。非易失性、无与伦比的写耐久性再配上快速数据采集能力,使FRAM成为下一代高级安全气囊系统的理想存储器工艺。

以前,汽车应用的主要非易失性存储器工艺是栅极悬空的器件,如EEPROM或闪存。栅极悬空器件都采用一SiO2薄层将多晶硅栅极与沟道隔离。对器件编程时,在控制栅极上产生高压使电子加速流向源极(N沟道器件)。因此,电子获得足够的动能穿透绝缘层,在多晶硅材料上被捕获(见图2)。

随着汽车设计要求复杂性的提高,栅极悬空存储器工艺的局限性越来越明显。例如,编程工艺要用几ms,对安全性很关键的应用这一时间太长了。对事故中出现的这种电源快速断电情况,栅极悬空器件能成功存储的信息几乎没有。

编程工艺对绝缘层也是破坏性的,因此,这类器件的写耐久性有限,通常为100,000~1,000,000个写操作。例如,在乘员传感器中,对这一上限值,其数据更新就太频繁了。假如写操作的典型要求是每秒1次,栅极悬空的器件工作不到12天就会毁坏。将数据缓冲到RAM中,再在掉电时写进栅极悬空的非易失性存储器会使EDR出现速度问题,不是一个真正的解决方案。

在智能安全气囊系统中,在碰撞事故中存储数据不仅必要,而且在事故前存储碰撞前的数据也很值得。使用轮询记录方法存储碰撞前数据最理想,但是对栅极悬空器件,这一方案证明是有问题的,原因是其耐久性有限。由于安全气囊模块用来储存能量以起爆安全气囊的电容很大,因此也会留有足够的剩余能量以在爆管起爆后从缓冲器写数据。能够写的数据量受可用能量的限制,就是说与电容器中残留能量和被写存储器的速度有关。典型的2K字节的栅极悬空存储器件写速度大约为4字节/5ms。因此,完整写栅极悬空存储器件要花1s以上的时间。

使用FRAM是一种方案,其FRAM的高耐久性和高速度能同时有效解决这两个问题。Ramtron的FRAM工艺将铁电材料和标准半导体芯片设计及制作工艺结合在一起,生产非易失性存储和模拟/混合信号产品。这些产品将高速读/写性能、几乎无限的写耐久性和静态RAM(SRAM)的低功耗,以及在电源丢失情况下标准RAM工艺所无法达到的安全存储数据的功能结合在一起。

FRAM电池采用工业标准的互补型金属氧化物半导体(CMOS)工艺制作,在两个电极板间的铁电晶体形成电容,类似于DRAM电容的结构。与易失性存储器给电容器充电来存储数据的方式不同,FRAM是将数据存储在铁电晶体内部。

给铁电晶体加上电场时,中心原子就向电场方向移动,随着原子移动到晶体内部,它穿过势垒,产生电荷尖峰信号。内部电路感测此电荷尖峰信号并复位存储器。如果将电场从晶体上移开,中心原子就呆在原位,保存存储器状态(见图3)。

- 富士通FRAM“上天入地”,拓展更多低功耗、高可靠性应用空间(08-06)

- 透过在ICT解决方案中使用FRAM技术降低整个系统的CO2排放量(10-22)

- 物联网数据处理网关的设计(03-14)

- STM32 使用 Flash 存储数据时的一种管理办法(11-13)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)