一种JPEG解码器低功耗解决方案

在整个图像解码过程中,每8×8个数据块中有约90%的数据的DCT系数为零,对这些零值进行IDCT变换并无意义。因此,本设计添加了零值判断逻辑来消除不必要的乘法运算。零值判断逻辑电路由8×8累加器阵列、零值判断逻辑模块和复选器MUX构成。通过零值逻辑模块判断,当操作数不全为零时,使能信号变成高电平,将操作数取到寄存器中,然后再进行乘法运算。如果操作数全为零,则封锁累加阵列,直接通过MUX输出0。零值判断逻辑能有效地降低功耗,且电路简单,面积与延迟时间几乎可以忽略不计。

3.2 基于锁存器的门控时钟

通过控制电路的输入时钟可以使得一部分电路降低工作频率或者停止工作,从而降低整个电路的功耗。2D DCT/IDCT的电路主要由3部分组成:1D DCT/IDCT单元、转置存储器、输入输出处理单元。

转置存储器部分只有在每次1D DCT/IDCT处理的最后才进行更新,而输入输出处理单元只有在数据输入输出的时候才工作。因此,控制这几部分电路的输入时钟,使其在大多数时间停止工作即可以有效地降低功耗。设计结果表明,在面积仅增加2%的情况下系统功耗可降低13%。

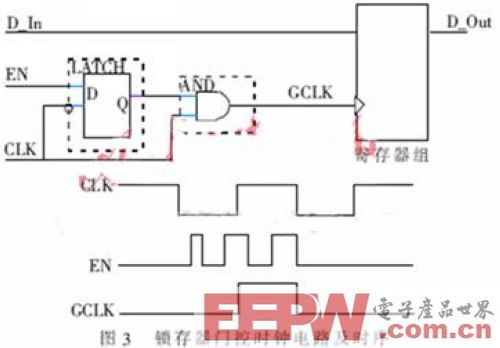

基于锁存器的门控时钟可以实现上述功能,它具有不需要数据选择器、面积较小、可以减小时钟网络上电容、减少门控寄存器的内部功耗等优点。锁存器门控时钟电路及时序如图3所示。

3.3 并行流水线

本设计使用加法和移位运算代替IDCT快速算法中的浮点乘法运算单元,用高度并行流水线VLSI结构加快数据处理速度,其处理数据的时间不到串行结构的1/5。因此,时钟频率可以相应地降低到串行结构的1/5左右,从而降低系统的功耗。例如,使用2个16×8的乘法器同时并行计算高位部分和低位部分,分别得到高位部分积和低位部分积,然后进行移位相加。实现电路运算时实现时间重叠、资源重复使用和资源共享,提高了系统的并行性,以此提高了乘法电路的运行速度和效率。

4 仿真和综合结果

本文选用1幅1 920×1 080大小的JPEG图像,Modelsim进行RTL级仿真后的波形如图4所示。图中JPEG_DATA是码流数据,OutR、OutG、OutB是解码仿真结果[4]。在100 MHz的频率下对解码核心模块进行综合[5],结果如表1所示。

本文有别于以往用软件实现JPEG解码,而是在用硬件实现JPEG解码的同时,改进硬件结构,通过多种易于操作的方法来降低硬件解码能耗。通过EDA工具验证,完全可以满足JPEG图像硬件解码的要求。

- JPEG2000核心算法的研究及DSP实现(05-23)

- 基于DSP的JPEG图像压缩的设计与实现(08-02)

- JPEG2000中53离散小波多层变换FPGA实现研究 (10-15)

- DSP在JPEG视频压缩系统的应用(01-04)

- 基于Android的3G手机网络摄像机客户端软件设计(02-29)

- 基于Blackfin561的JPEG2000压缩算法实现(03-23)