JPEG2000中53离散小波多层变换FPGA实现研究

摘要:基于新一代图像压缩国际标准JPEG 2000,介绍一种快速、有效的多层5/3小渡变换的VLSI设计结构,该方法使用两组一维变换实现,用移位-相加代替乘法操作,整体设计采用了流水线设计。利用双端口RAM和地址生成模块的调度完成小波变换的分裂、边界延拓工作,不需另外增加模块。二维离散小波变换滤波器结构的设计采用Verilog HDL进行RTL级描述,已经通过了FPGA验证,并可作为单独的IP棱应用于图像编解码芯片中。

关键词:JPEG 2000标准;离散小波变换;FPGA;RAM

0 引言

随着多媒体应用领域的快速发展,新一代静止图像压缩标准JPEG 2000己在2000年11月完成了标准的制定。与原有的JPEG标准相比,JPEG 2000具有许多优势。例如更高的压缩性能,支持单分量或者多分量的有损和无损压缩,可以提供质量和分辨率渐进传输,以及感兴趣区域编码等。典型的JPEG 2000编码中的传统的离散小波变换由卷积完成,因此在实现中需要巨大的计算和存储量。I.Daubechies和W.Sweldens等人提出的提升算法解决了这些问题,该算法采用采用移位-相加操作代替卷积操作,大大降低了DWT运算硬件实现的难度,因此JPEG 2000采用基于提升的DWT作为图像压缩的第一步。JPEG 2000推荐5/3及9/7小波分别用于无损和有损压缩,本文针对5/3滤波器,提出了一种高效高速的二维三层小波变换的硬件平台,整体结构采用流水操作。

1 离散小波提升算法

离散小波提升算法主要有三个步骤:分裂(Split)、预测(Predict)和更新(Update)。分裂是把输入信号x(n)分成奇偶两个子信号集,即由其采样后的偶序列子信号组成xe=x(2n),奇序列子信号组成x0=x(2n+1)。预测是偶序列信号乘上一个预测参数P,来预测奇信号,原来的奇序列信号与预测值的差即为高频系数d(n)。更新是高频系数乘以更新系数Q与偶序列信号的和,获得低频系数s(n)。

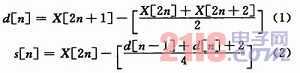

5/3双正交小波对应的提升方法如图1所示,用于JPEG 2000中的无损压缩过程,硬件实现可分为两步,如式(1),式(2)所示:

2 5/3小波内嵌延拓提升算法

由式(1)和式(2)可以看出,在图像边界处进行小波变换时需要进行延拓处理,否则无法正确进行小波变换,对原始图像边界数据的处理通常使用对称周期延拓方式,5/3小波变换的延拓需要在序列前延拓两个数据,在序列后延拓一个数据,图2为5/3小波变换时8点数据序列周期对称延拓示意图。

本文是通过双端口RAM的读/写实现分裂过程,在小波变换过程中通过对读地址的操作实现对称周期性数据延拓:用对计数器的计算操作实现边界数据延拓和生成读取地址与写入地址,从原图像中读取,经变换后写入相应的地址,以8×8图像为例,行方向上延拓后的读取地址顺序应该是2,1,0,1,2,3,4,5,6,7,6,10,9,8,9,10,…;列方向上延拓后读取地址顺序是16,8,0,8,16,24,32,40,48,56,48,17,9,…。

3 硬件设计

3.1 总体结构框图

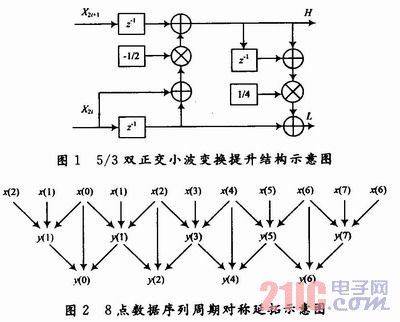

二维DWT实质上相当于先对图像数据做一维行方向小波变换,再对变换后的结果进行一维列方向上的小波变换,总体结构如图3所示。输入的图像数据是在原始RAM上存储,通过行地址模块生成的行变换地址读出图像数据,通过一维行向量的小波变换模块处理,将中间数据放入中间RAM中,再通过列地址模块生成的列变换地址读出中间图像数据,通过一维列向量的小波变换模块处理,最后将输出的小波分解系数写入外部存储器,然后由控制单元判断是否进行下一级小波分解,如果需要做下一层分解的话,将在上一层小波变换的结果中取出LL低频子带进行下一个循环,每对图像进行一次二维小波变换,产生的结果同样存储在外部存储器IM-RAM上,即下一级的小波变换结果覆盖在上一级的LL子带上。

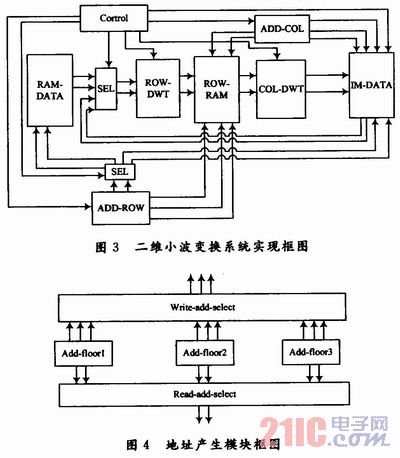

3.2 地址生成模块的设计

对于做三层的离散小波变换,每层对RAM的(行/列)读/写地址都不相同,所以在地址生成模块中分别做了三层各自的地址模块,每个单层地址模块产生2路读地址信号、2路写地址信号和1路写地址使能信号。首先产生行变换的读/写地址,在行变换完成之后产生列变换的读/写地址,在列变换完成之后,给出一个EndOfBlock信号返回给图4中的Control模块。由Control模块控制分层地址模块的使能以及Select模块选择有效地址信号输出,并且通过对读地址计算算法的调度,实现分裂和边界延拓功能,不需要另外设计单独的处理模块,地址生成模块的总体框图如图4所示。

4.功能仿真及FPGA测试验证

该设计采用了流水线技术即通过插入寄存器,使得一组输入数据的计算分布在同一个时钟周期中,从而提高资源利用率,增加电路的数据处理量,提高了性能,在此用Verilog HDL描述实现。

4.1 功能仿真

在ModelSim的测试模块中设置时钟为100 MHz,图5为部分仿真结果,输入数据在经过3个时钟周期后计算出LH分量输出。由此可见,一维小波变换模块的设计符合JPEG 2000标准规定,结果正确。

- JPEG2000核心算法的研究及DSP实现(05-23)

- 基于DSP的JPEG图像压缩的设计与实现(08-02)

- DSP在JPEG视频压缩系统的应用(01-04)

- 基于Android的3G手机网络摄像机客户端软件设计(02-29)

- 基于Blackfin561的JPEG2000压缩算法实现(03-23)

- 基于JPEG2000小波提升在DSP上的缓存管理(05-14)