为什么高速USB并不一定表示手机拥有高速性能

挑战之一是将数码多媒体传输到设备自身。由于USB对于PC的普遍性以及便携性,USB成为多媒体传输的必然选择。用户可以很容易地使用USB来传输多媒体、同步数据,并且为他们的设备充电,进一步巩固了其作为手机接口标准的地位。但是,许多第一代设备仅支持全速USB,数据传输速度不超过12Mbps。使用全速USB,需要用一个小时将数据从100 MP3传输到其它设备。该数量级的等待时间对于消费者来说是无法接受的,他们需要更快的传输速度。随着手机的多媒体功能从单一的音乐功能发展到电影以及更高需求,随着数据和存储容量的增长,需要更快的传输接口。业内对此挑战的解决方案便是出现了高速USB,最大理论传输速率可达480Mbps——比全速USB速度要快40倍。

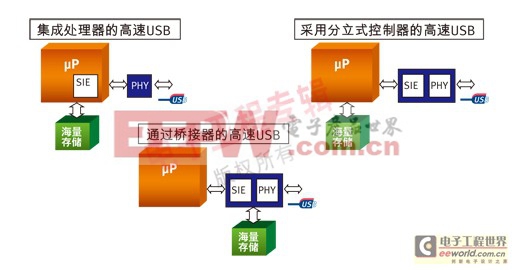

可供选择的几种高速USB架构

随着高速USB成为新型多媒体中心手机的基本需求,设计者可以选择几种不同的架构来支持高速USB。

第一种选择(若可行)是在所选的处理器内使用高速USB逻辑。在这种架构中,直接由处理器支持高速USB,外接USB收发器用于物理层通讯。典型情况下,USB收发器为处理器的外接设备,从而节省住处理器内的硅面积。由于USB收发器的模拟属性,当向更小尺寸技术发展时,例如65nm及以下,不能达到数字技术规格。将模拟元件(例如USB收发器)外接通常会降低成本并且有效利用空间。

第二种选择是使用单独的高速USB控制器。该器件包含了支持高速USB需要的所有部分,包括SIE和收发器。这些器件通常通过存储接口连接到主机处理器。

第三种选择是使用桥接器,可以在其它特性内包含高速USB功能,例如海量存储控制。与专用高速USB控制器类似,这些设备通常通过处理器存储接口进行连接。

性能对比

我们快速看一下手机市场,可以发现手机的选择范围很大。现代手机的范围可以从简单的单一功能到复杂的多功能智能手机。由于音乐手机的普及性,驱使在现在的手机中广泛采用高速USB。同时,手机也普遍支持海量存储,并提供多种选择。对于手机的高速USB设计,上述3种架构均适用。

由于高速USB的最大理论性能可达480Mbps,在实际的应用中,由于软件架构的限制,达不到最大理论性能。高速USB的架构和设计是实际性能的重要决定因素。

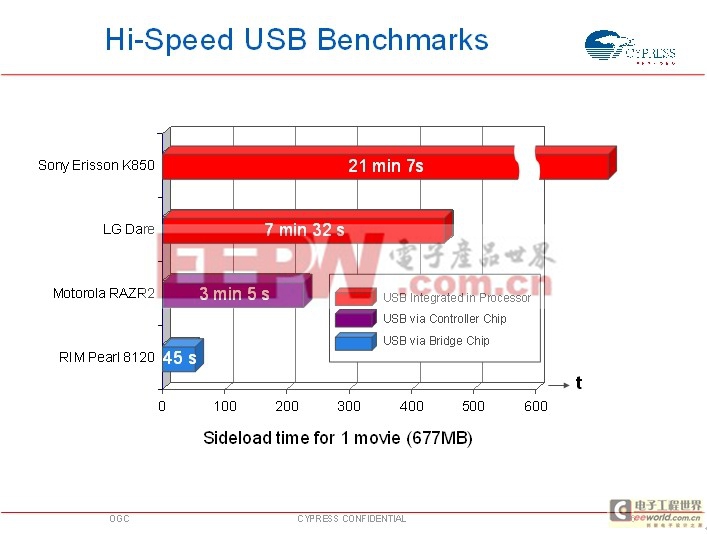

下面我们看一下具有高速USB的一些手机(高速USB的实现方式不同)的USB性能对比。在相同环境下的各手机中,用户将677MB的视频文件传输到手机上的海量存储区。为了保证一致性,在所有应用中采用了海量存储模式和相同的移动式海量存储。可以从下面的示意图中看到该对比的结果。

图1:支持高速USB的三种不同架构。

内部结构

我们可以从上述结果看出,实际的高速USB性能变化范围很大。从超过20分钟(低于10Mbps)的传输时间到不超过1分钟(超过140Mbps),相差25倍以上。为什么差距会如此之大?其答案在于USB的架构不同。

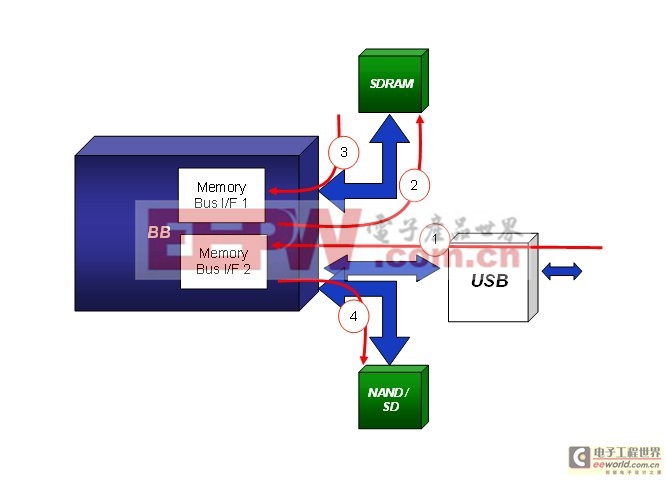

在使用单独的高速USB控制器的架构中,控制器通常通过主处理器外接存储接口连接到处理器。通常与存储设备共享此接口,例如NAND,NAND可用于代码或用户数据存储。从主机输入的数据通过USB控制器传输到主处理器。该点的处理器在将数据写入海量存储前先缓存到SDRAM。整个过程分多步完成,需要占用大部分处理器,从而限制了USB的传输性能。在下面的示意图中描述了这种应用的数据流。

图2:部分手机(高速USB的实现方式不同)的USB性能对比。(高速USB对比、 1部电影的传输时间)

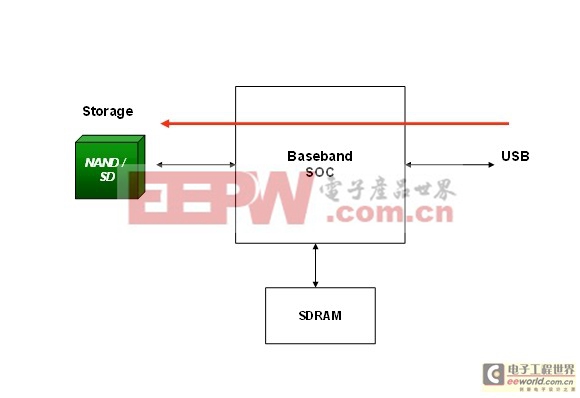

高速USB实现的另一种可选架构是使用集成了USB控制器的处理器。许多支持高速USB的处理器还具有多个CPU内核,以提高处理能力,例如音乐和视频。在下面的示意图中显示了这种应用的理想的数据路径。

图3:使用单独的高速USB控制器的高速USB的数据路径。(存储总线)

由于USB控制器集成在处理器中,理想情况是数据直接从USB传输到海量存储。然而,数据从USB到海量存储的实际传输路径并不是描述的那样直接传输。在下面的示意图中显示了处理器中的实际数据流。

图4:使用集成了USB控制器的处理器来实现的高速USB理想的数据路径。

从该示意图中,可以看到一个CPU内核用于控制USB SIE,另一个CPU内核用于海量存储控制器。所有内核共用相同的SDRAM,SDRAM被分成两个内存,专用于各CPU内核。由于CPU内核不能访问其它CPU内核的内存,CPU1必须将数据缓存,然后将数据发送到CPU2,并且在写入存储区前在CPU2中进行缓存。该过程会带来很大的系统负荷,影

- STM32F407高速USB口速度测试(11-23)

- 一种高速USB设备控制器IP核的设计与实现(08-31)

- 高速USB IP核的设计与开发(08-31)

- 基于嵌入式系统的手机编程开发平台(07-30)

- 五大主流智能手机操作系统的前世今生(03-02)

- Linux手机研发要过五大难关(03-07)