基于AMBA总线接口的AFDX端系统IP核

1 引言

本文介绍了基于AMBA总线接口的AFDX端系统IP核的设计方案,使AFDX端系统的应用不只局限于终端板卡的形式。在片上系统(SoC)芯片中集成AFDX端系统功能,使AFDX端系统的应用更加灵活,以满足不同的应用需求。基于S698-P4的SoC系统芯片是珠海欧比特公司自主研发的一款32位嵌入式SoC芯片。应用该芯片集成了一个符合ARINC664规范[4]的AFDX端系统IP核,目前该IP核设计已经通过了RTL级验证和FPGA验证。

2 AFDX端系统

AFDX端系统嵌入在每个航空电子子系统中,主要提供航空电子设备子系统和AFDX互联网络之间的接口,负责消息的发送和接收。AFDX网络不同于普通以太网的特性主要由端系统实现[5],主要包括:

2.1 虚拟链路

AFDX引进了虚拟链路(Virtual Link,VL)对带宽资源进行有效地分隔。虚拟链路是AFDX网络的核心,每条虚拟链路都在源端系统和目的端系统之间建立一条单向逻辑链路来传输数据,同时还允许建立子虚拟链路。在发送端采用流量整形机制通过对每条VL定义最大帧长度Lmax(Maximum Frame Size)和带宽分配间隔(Bandwidth Allocation Gap,BAG)在VL间分配通信资源。

流量整形功能是在单条虚拟链路上调整帧的发送时间,使每条虚拟链路在各自的BAG内只能发送一个帧。ARINC664第7部分规定AFDX网络集成者需要根据实际应用需求为每条虚拟链路预先配置BAG,BAG的取值需要在1ms~128ms范围之内,同时满足公式:BAG = 2k (单位:ms),(k的取值范围是0~7)。

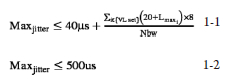

端系统的每个VL的Max_jitter(最大允许抖动)应该服从下列两个联立的公[4]:

2.2 冗余网络

AFDX采用冗余网络增强数据传输的可靠性,以保证在某一个网络崩溃时仍可以继续正常通信。在冗余配置下,对发送的数据帧进行编号,并将它复制成两份,分别通过物理上相互独立的网络向目的端系统发送。端系统具有冗余管理功能,目的端系统根据编号按顺序接收。如果两个冗余帧都被正常接收,则后到的被丢弃;如果其中一个出现传输故障,则可以用另一个进行替代。

3 AMBA总线

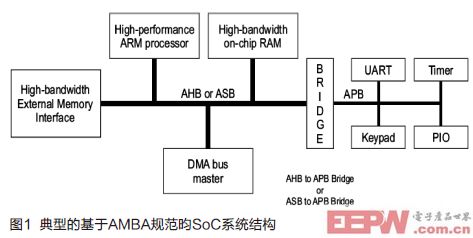

AMBA规范[6]是ARM公司设计的一种用于高性能嵌入式系统的总线标准。AMBA规范定义了3种可使用的不同类型的总线:AHB,ASB和APB。

典型的基于AMBA的SoC系统结构如图1所示[7]。其中高性能系统总线(AHB或ASB)主要用以满足CPU和存储器之间的高带宽要求。CPU、片内存储器和DMA设备等高速设备连接在其上,而系统的大部分低速外部设备则连接在低带宽总线APB上。系统总线和外设总线之间用一个桥接器进行连接。

4 AFDX端系统IP核设计

4.1 AFDX端系统IP核体系结构

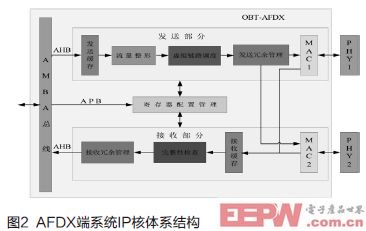

系统集成的AFDX端系统IP核符合ARINC664规范。该IP核通过AMBA总线与RISC核通信,通过外接一个物理层PHY接口芯片与AFDX网络相连。AFDX端系统IP核主要技术特征包括:(1)支持ARINC664规范;(2)高性能的AMBA总线接口与RISC间的数据传输;(3)提供2个10/100M的RJ45形式的AFDX端口,支持2个端口独立使用或2个端口互为冗余;(4)软件实现传输层(UPD)、网络层(IP)协议,硬件实现链路层(Virtual Link)及物理层(PHY)层协议 ;(5)硬件实现快速传输调度和虚拟链接过滤 ;(6)支持采样(Sampling)和列队(Queuing)端口;(7)支持发送和接收各128条虚拟链路(VL)。AFDX端系统IP核体系结构如图2所示。

AFDX端系统IP核内部主要有:AMBA总线接口模块、发送功能模块、接收功能模块、媒体介质管理模块(MAC)、寄存器配置管理模块。

4.2 AFDX端系统IP核中关键模块设计

4.2.1 AMBA总线接口模块

该模块实现了AFDX端系统IP核与RISC间通信功能。当发送或接收数据帧时,总线控制器都要访问AMBA总线上的SRAM,以读或写数据,此时AFDX端系统IP核作为总线Master访问SRAM(通过AHB总线)。当RISC核(作为总线Master)访问AFDX端系统IP核寄存器时,该IP核作为总线Slave响应总线Master的传输请求(通过APB总线)。

在发送一个数据帧时,RISC核首先写寄存器以允许AFDX端系统IP核发送数据帧,然后构建好发送缓冲区描述符(TxBD)并写入SRAM。发送控制器读取该TxBD并启动AHB Master从SRAM中直接读取数据存放到内部的发送缓存RAM,并最终产生发送控制信号(TxCtrls)通知发送模块等待调度发送。其中,发送缓存分成128个存储空间,根据不同的虚拟链路号(VL)来存储128个虚拟链路的发送数据。接收数据帧的过程类似。

4.2.2 发送功能模块

发送模块要实现以下功能:按照端系统的配置,对各条虚链路的数据帧进行流量整形;在各虚链路之间进行调度以多路复用物理带宽;然后添加序列号SN,再根据配置信息中各虚链路的冗余状态,将其帧发往MAC A、MAC B模块。发送模块主要功能如

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- TM1300 DSP系统以太网接口的设计(03-07)

- 工业级特性在嵌入式处理中至关重要(05-08)

- 基于VxWorks的双端口网卡智能双冗余驱动(07-01)

- 基于μC/OS-II和TCP/IP协议的多串口服务器(08-23)

- 基于DSP/FPGA的以太网控制器的运动控制器设计(02-06)