一种基于FPGA的多通道高速采样系统设计

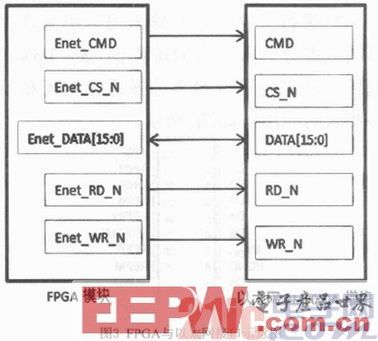

功耗非常低,单电源3.3V工作,内置3.3V变2.5V电源电路,I/O端口支持3.3~5.0V的容差。FPGA与以太网的接口示意图如图3所示。

3 多通道并行处理

由于FPGA具有并行处理的优势,在高速多通道同步采样中,更能满足设计的要求。选择硬件描述语言为Verilog,它能够在多种抽象级别对数字逻辑系统进行描述,可以显式地对并发和定时进行建模。本设计是四片AD芯片的同步高速采样,利用FPGA具有的自定义外设以及自定义指令的功能,对于四片AD芯片实现了同步采样的控制,并对数据并行处理。

3.1 单片ADC的控制

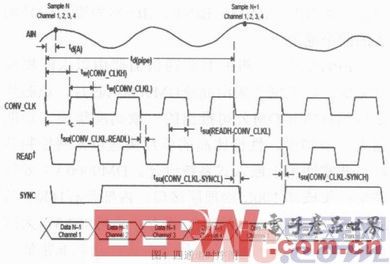

AD芯片THS1207的单通道采样的最大采样速度是6MSPS,四通道采样的最大采样速度是1.5MSPS,本设计采用的是四通道同步采样模式,四通道时序图如图4所示。

在转换过程中ADC有一个自由运行的外部输入时钟CONV CLK。随着每一个CONV CLK信号下降沿,四个通道模拟信号转换后的值提供给相应的读出信号中的数据总线。READ+是,CS1三者的逻辑集成信号,READ+为低电平时表示读有效。信号SYNC是低电平时,第一个通道的数据到数据总线,随后SYNC拉高,第二、三、四通道的数据按顺序依次读取。

3.2 多片AD的同步采样及并行处理

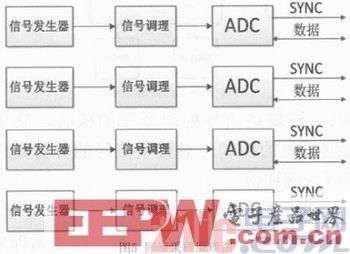

单个AD的控制完成后,就很容易扩展到对四片AD的控制。在采集多通道数据时,需要保持同步采样,本设计采用的方法是每一路信号通过各自的信号调理电路和ADC转换结束后,ADC保持数据,由FPGA依次读取。

在硬件布局时,四片AD共用数据线,读写信号和AD转换时钟信号。因此FPGA通过写命令同时启动这四片AD芯片,十六个通道的模拟信号进入AD。每片AD都有一个数据同步信号SYNC,当判断得到四片AD中的某个SYNC信号是低电平时,则可认为十六道数字信号已同步到位,通过片选信号的切换依次读取各个AD芯片的数据并暂时储存在寄存器中。也可以根据自己需求,开启和关闭某些AD,选择特定的通道数据进行读取。同步采样原理图如图5所示。

3.3 自定义指令

自定义指令是FPGA的嵌入式软核nios ii的一大特色,nios ii有着一个开放式的ALU,用户可以根据自己的要求添加自定义指令来实现应用需求,大大体现了nios ii软核的灵活性。自定义指令的功能是运用Verilog语言,由电路模块来完成的。因此,相比较利用C语言编程来实现功能,自定义指令具有执行速度快的显著特点。Nios ii支持四类自定义指令:组合逻辑指令、多周期用户自定义指令、扩展用户自定义指令、内部寄存器自定义指令来满足各种应用情况。

本设计中旋转机械的振动信号虽然在硬件中经过了信号调理,但是由于元器件间参数的问题,仍旧会存在数据的偏差,运用了自定义指令中的多周期用户自定义指令将数据进行修正。多周期指令需要数据指令和逻辑指令。利用start信号开始执行指令,done信号来表示执行结束,可以返回结果。

同时对于采集得到的数据进行傅里叶变换、滤波等处理,通过自定义指令也能实现,提升了FPGA的信号处理能力。

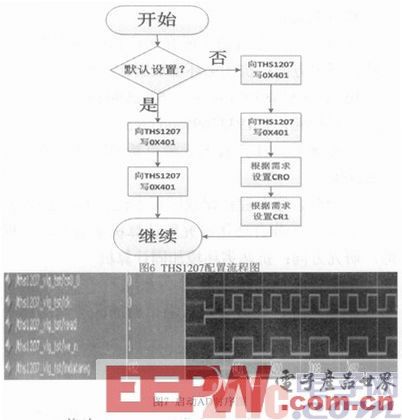

4 AD时序仿真

仿真在FPGA的开发中扮演了重要的角色,利用modelsim仿真软件来对编好的AD程序进行时序验证。AD正式工作前,需要通过向AD内部控制寄存器、CR1写命令启动AD,然后才能读取数据。启动AD芯片THS1207的流程图如图6所示,启动AD的仿真结果如图7所示。

AD芯片THS1207正常启动后就可以开始读取各个通道的数据,由于本设计是十六个通道依次采样,采样结束后,需要通过片选控制信号依次读取各个通道的数据,仿真结果如图8所示。

从仿真结果验证得到编写的AD程序可以完成十六道采样的设计要求。

5 实验结果

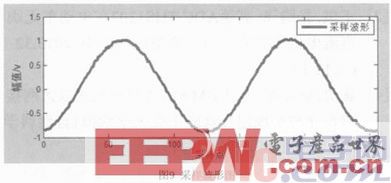

实验采用AD四通道同步采样,利用信号发生器产生正弦波,选择同步采样方式对每个正弦波采样128点,通过以太网传送到上位机,采样得到的波形如图9所示。

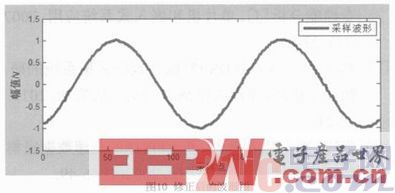

可以利用FPGA的自定义指令,根据需求将得到的数据进行处理,如图10,对得到的波形数据进行偏置为-10和放大倍数为1.05的修正。

实验中当信号发生器发出正弦波的频率达到3000Hz时,即采样频率达到384kHz时,FPGA采集波形能力达到了最大值,相当于180000r /min的旋转机械的基频信号。当超过3000Hz时,采样得到的波形会出现毛刺现象。分析原因,主要是由于nios ii进、出中断服务程序,以及中断服务程序中对采样数据的读取需要花费一定的时间。

6 结束语

本设计利用FPGA并行技术、自定义模块化设计以及nios ii的特色功能即自定制指令,实现了对于旋转机械振动信号的多通道高速同步采样。显示了FPGA可编程、设计灵活、高速的特点,同时也验证了基于FPGA的多通道高速采样系统的可行性。

根据实验结果和理论的最大采样速度还有差距,

FPGA EP3C25Q240 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)