DSP与PC机串行通信接口设计及应用

引言

tms320f24x是美国ti公司tms320系列定点数字信号处理器(dsp)之一,tms320f240是f24x系列面向数字控制芯片的典型代表。由于tms320f240并不具备人机界面,在实际使用过程中,需要为它提供一个人机接口或上层控制接口,以便于观察控制效果或传递必要的控制信息。因此,实现tms320f240与pc之间串行通信接口的设计方法,具有较高的实用价值。

串行通信接口的硬件设计

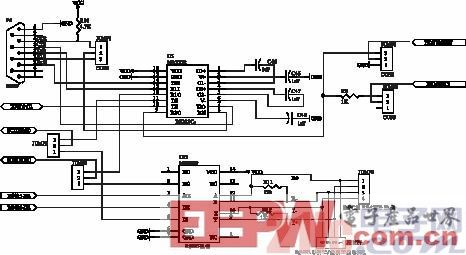

f240芯片内部集成了一个串行通信接口(sci)模块,该模块是一个标准的通用异步接收/发送(uart)通信接口,通信接口有scitxd(sci发送输出引脚)和scirxd(sci接收输入引脚)两个外部引脚,引脚的信号电平为ttl类型。而pc机串口的异步串行通信基于rs232c标准,两者的信号逻辑电平不一致,必须进行信号电平转换。选用内部含有电压倍增电路的电平变换芯片max232,max232有两对收/发单元,实现dsp与pc之间的串口通信只需一对收/发单元即可,在完成dsp与pc的正常通信任务的基础上,利用另外一对收/发单元,扩展了实现 pc与dsp的双向复位功能。当dsp控制器程序出错、监控对象异常或需要控制程序重新运行时,可以直接从上位pc发控制指令,达到复位下位机的功能。同样,也可以从dsp端复位pc或给pc发特定的命令信号。dsp与pc串行通信接口的硬件设计如图1所示。

以rs232c通信标准进行通信,在保证通信准确性的前提下,通信距离一般以不超过12m为宜,在工业控制现场很受限制。为保证硬件设计的兼容性和易扩展性,能够应用于不同场合,在dsp硬件电路板端还采用了一个max489芯片,添加了一个rs485/rs422通信接口。

实际使用过程中,系统在选择不同的通信标准时,切换十分方便。如图1所示,当跳线端子jump2与jump3的2、3脚短接时,scitxd接通 max232芯片的t1i引脚,scirxd接通max232芯片的r1o引脚,即dsp的通信接口与max232芯片相连,此时系统采用rs232c的通信标准。当跳线端子jump2与jump3的1、2脚短接时,scitxd接通max489芯片的di引脚,scirxd接通max489芯片的ro引脚,即dsp的通信接口与max489芯片相连,此时系统采用rs485/422的通信标准,pc端只需添加一个rs232c/rs485转换器即可进行通信接口电平转换。

通信接口的软件设计

● 通信协议的设定

uart通信对噪音比较敏感,特别是脉冲边沿抖动。所以,为了确保uart能够正确工作,必须能够检测它的开始和结束字节。也就是说,需要一定的数据包格式,即使是使用一个uart端口,在这个数据包中的每一个字节也都要编成uart格式。因此在异步串行通信中,收、发双方必须事先规定字符格式、采用的波特率,以及时钟频率和波特率的关系。

这些规定是通过初始化设置与串行通信有关的寄存器来实现的。本通信系统中,规定字符格式为:每一帧的数据占10位,一位奇校验位,8位数据位,1位停止位。中间的8位数据位即为有效的通信传输字节。双方的波特率设置为19200bps。同时,为了增强通信的可靠性,减少通信的误码率,规定了通信双方收发数据包的协议如表1所示。

特征码选用0xff、0xaa、0x55这3字节为发送数据包的前导数据,这是因为这几字节在传输噪声中同时出现的几率很小,特征码起到向接收方表明有数据发送过来的作用,通知接收方可以开始接收有效数据;字节数是数据包中除了字节数这一项之外,其他所有项字节的长度;有效数据字符串是通信发送方要传送的有效数据;校验和是数据包中除了校验和这一项之外所有项字节的无进位累加和,用于校验通信是否正确。

同时,在通信过程中约定了双方的软件握手方法。为了不使通信过于复杂,提高通信速度,可以直接将握手信号0xff嵌入到数据包中。软件握手协议规定如下:pc定时发送符合通信协议规定的数据包,dsp接收到的第四字节若为握手信号0xff,则将校验正确后的有效数据存储,并从中分解有效字节信息,然后回送相同格式的数据包。若pc接收到的数据包的第四字节不是0xff,则摒弃该数据包。dsp与pc的通信流程图如图2所示。

● dsp端下位机sci通信程序的编制

在dsp端的软件程序设计中,通过中断方式接收pc发送过来的数据包,握手并校验确认后接收有效数据,再将pc所需的数据打包回送。基于dsp功能模块化的特点,其串行通信汇编程序的编制主要分三个步骤:

(1)初始化设置时钟源模块,得到所需的cpuclk和sysclk(因为计算波特率时与之有关);

(2)设置sci模块,初始化各sci控制寄存器;

(3)编写串行通信中断服务子程序,即可完成dsp与pc之间的串行通信。

在串行通信中断服务子程序的编制过程中,参考图2所示的dsp与pc串行通信流程图,即可完成正常的

ti tms320f24x 相关文章:

- Linux标准趋向统一(11-12)

- 巴西的新电视机顶盒采用意法半导体(ST)的最先进的解码器技术(03-24)

- 基于TMS320C62X DSP的混合编程研究(07-12)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 展望未来 多核DSP技术不仅仅是小把戏(04-03)

- 嵌入式软件工程师必须知道的:volatile的作用(05-01)