基于SDRAM芯片立体封装大容量的应用

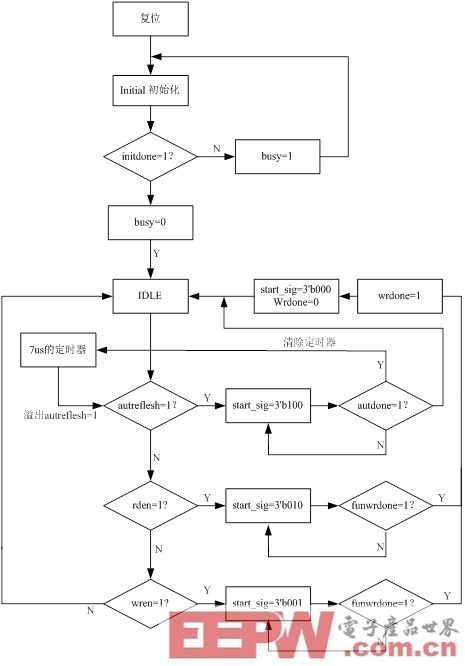

,首先要完成初始化模式设置,当初始化模块完成初始化输出initdone时,逻辑控制部分输出busy=0,表示初始化完成了。接着进入空闲IDLE状态,在这个状态中进行刷新autreflesh、读rden和写wren的检测。当检测到autreflesh=1时,表示要进行刷新动作置start_sig=3’b100启动刷新功能,刷新完成之后得到反馈信号autdone=1,之后清除定时器,置start_sig=3’b100让功能模块状态变量回到空闲IDLE状态,并且回到逻辑控制部分的空闲状态。当检测到rden=1时,置start_sig=3’b010启动读功能,等到funwrdone=1读完成时,置start_sig=3’b000让功能模块状态变量回到空闲IDLE状态,并输出一个wrdone的正脉冲表示读功能完成,然后回到逻辑控制部分的空闲状态。当检测到wren=1时,置start_sig=3’b001启动写功能,等到funwrdone=1读完成时,置start_sig=3’b000让功能模块状态变量回到空闲IDLE状态,并输出一个wrdone的正脉冲表示写功能完成,然后回到逻辑控制部分的空闲状态。刷新读写功能的检测是有顺序的,也就是说是有优先级的,刷新比较重要,不立即数据就会丢失,所有首先检测刷新动作,相对来说读写并没有比较明显的区别,本案例读的优先级比写的优先级高。

图12 逻辑控制部分流程图

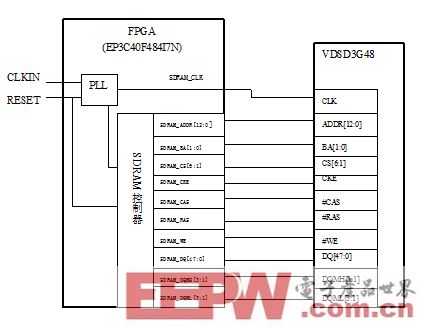

2、 FPGA与VDSD3G48的硬件连接

FPGA与VDSD3G48硬件连接图

如图所示,FPGA输入CLKIN时钟和RESET复位信号,其中复位信号能够复位锁相环PLL和SDRAM控制器,时钟输入经过PLL倍频之后一路送给SDRAM控制器,另一路送给输出送给VDSD3G48。FPGA的SDRAM_ADDR[12:0]、SDRAM_BA[1:0]、SDRAM_CS[6:1]、SDRAM_CKE、SDRAM_CAS、SDRAM_RAS、SDRAM_WE、SDRAM_DQ[47:0]、SDRAM_DQMH[3:0]、SDRAM_DQML[3:1]分别与VDSD3G48的ADDR[12:0]、BA[1:0]、CS[6:1]、CKE、#CAS、#RAS、#WE、DQ[47:0]、DQMH[3:1]和DQML[3:1]相连。

结 语

对于同步随机动态存取存储器(SDRAM)堆叠而成的立体封装的大容量存储芯片VDSD3G48,要进行初始化和刷新操作才能保证访问的正确性。同时基于SDRAM芯片立体封装存储器缩短了内部信号连接长度、减少了寄生效应,增强了抗干扰能力,可广泛用于车辆、卫星、飞机和空间站等领域。

- μClinux下SDRAM数据交换区的生成和使用(06-04)

- 基于DSP的数码望远相机的研究与设计(03-28)

- DSP片外高速海量SDRAM存储系统设计(01-18)

- 基于DSP片外高速海置SDRAM存储系统设计(03-12)

- DSP片外高速海置SDRAM存储系统设计方案(06-13)

- FPGA最小系统之:最小系统的概念(06-05)