基于SDRAM芯片立体封装大容量的应用

隔也是不同的,计算方法是:刷新间隔时间=64ms/行数。VDSD3G48有每片基片有8192行,刷新间隔时间T=64ms/8192=7.8125us,考虑到余量,取7us。

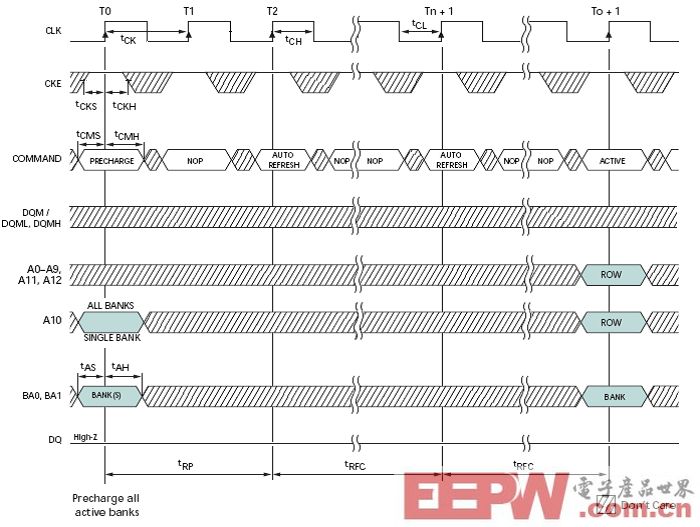

在发REFRESH命令之前,必须发PRECHARGE命令释放所有选中的banks。接着要等到TRP的延时之后才发REFRESH命令。所刷新单元地址由内部刷新控制器产生,所有REFRESH命令不用输入地址信号。所有操作如图7自动刷新时序图所示:

图7自动刷新时序图

1.3.3单个自动预充电写

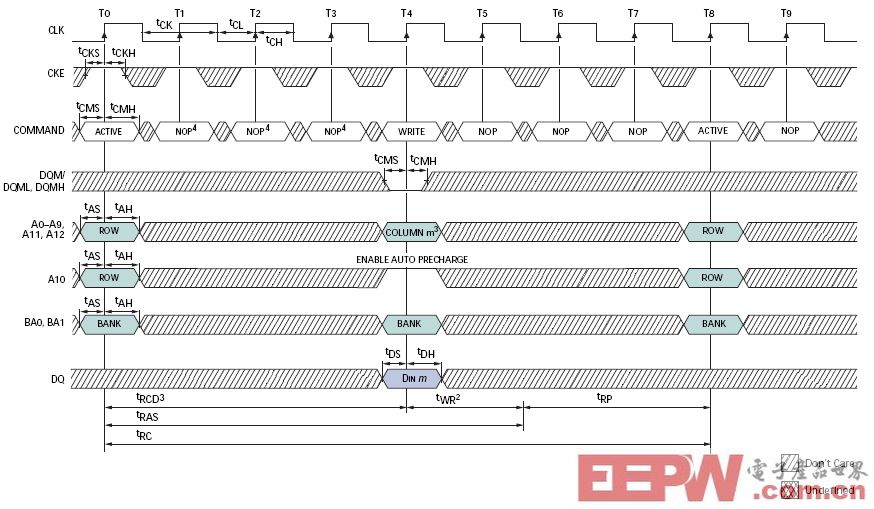

在写过程中,ACTIVE命令用于锁存来自A[12:0]的地址信号和来自BA1、BA0的bank信号,WRITE命令锁存来自A[9:0]地址信号,如果DQM为低,则来自DQ[47:0]上的数据则存入存储器阵列;如果DQM为低,来自DQ[47:0]上的数据将不忽略。A[10]用于选择是否自动预充电,如果选择,那么在写完成后选择的行将预充电。操作如图8单个写时序图所示:

图8单个写时序图

1.3.3单个自动预充电读

在读过程中,ACTIVE命令用于锁存来自A[12:0]的地址信号和来自BA1、BA0的bank信号,READ命令锁存来自A[9:0]地址信号。数据的输出将根据DQM信号的输入而定,在READ命令期间如果DQM为低,那么在经过两个时钟之后将输出数据(CAS Latency=2);如果DQM为高,那么将输出高阻态。A[10]用于选择是否自动预充电,如果选择,那么在读完成后选择的行将预充电。操作如图9单个读时序图所示:

图9单个读时序图

1.3.4 VDSD3G48控制器的实现

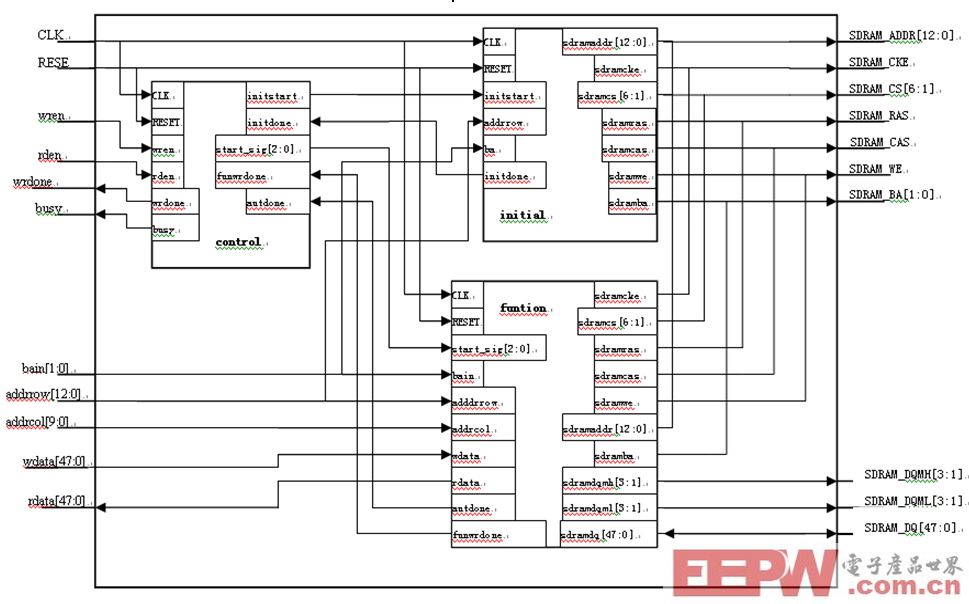

本案例的控制器只实现单读单写功能。即便如此,初始化模式设置和刷新功能是必不可少的。控制器原理框图如图10所示:

图10控制器原理框图

控制器分三部分:control逻辑控制、initial初始化和funtion功能部分。initial部分主要完成初始化模式设置;funtion部分主要完成刷新、读和写功能;control逻辑控制部分主要是控制协调initial初始化和funtion功能部分。

各个信号说明如表2所示:

表2 控制器信号说明

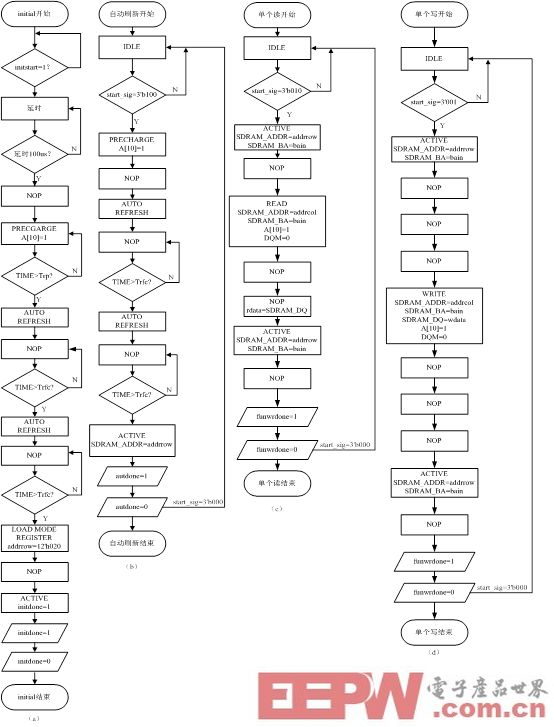

initial初始化

按照图4初始化和模式设置时序图,在初始化过程中,首先要延时100us,以便VCC和CLK稳定,接着发送NOP命令,再接着发PRECHARGE命令,此时发送A[10]=1,表示选择所有banks。延时tRP时间后发送AUTO REFRESH和NOP命令,如果延时大于tRFC,那么再发AUTO REFRESH和NOP命令。延时tRFC时间后发LOAD MODE REGISTER命令,地址信号送入设置的模式数据,之后发NOP命令,最好发ACTIVE命令,并送入行地址和bank信号。操作如图11(a)initial流程图所示:

图11(a)initial流程图 图11(b)自动刷新流程图

图11(c)单个读流程图 图11(d)单个写流程图

自动刷新

按照图7自动刷新时序图,FPGA实现自动刷新可按照图11(b)自动刷新流程图来实现,共有十个状态:IDLE、PRECHARGE、NOP、AUTO REFRESH、NOP、AUTO REFRESH、NOP、ACTIVE、autdone=1和autdone=0。这里并没有把NOP、AUTO REFRESH合并是因为不想增加难度。另外,ACTIVE和autdone=1也可以放在同一个状态中。自动刷新功能是由start_sig=3’b100发起的,之后就是按照十个状态按顺序进行。autdone=1和autdone=0两个状态在读时序中并没有出现,应用案例用着两个状态来产生一个正脉冲表示自动刷新动作完成了,用于各个部分协调。最后当start_sig=3’b000时返回IDLE状态这个动作很重要,因为自动刷新、读写操作都是用同一个状态变量,当刷新完成时状态变量处于autdone=0这个状态,假如刷新完成之后进行读操作,那么最终只进行了autdone=0这步操作,而不是从IDLE到autdone=0一系列的操作。其他操作原理同样如此

单个读操作

按照图9单个读时序图,FPGA实现读操作可按图11(c)单个读流程图来完成。实现共有十个状态:IDLE、ACTIVE、NOP、READ、NOP、NOP 、ACTIVE、NOP 、autdone=1和autdone=0。单个读功能由start_sig=3’b010发起的,之后就是按照十个状态按顺序进行。autdone=1和autdone=0两个状态产生一个正脉冲表示读动作完成了。最后当start_sig=3’b000时返回IDLE状态。

单个写操作

按照图8单个写时序图,FPGA实现写操作可按图11(d)单个写流程图来完成。实现共有十个状态:IDLE、ACTIVE、NOP、NOP、NOP、WRITE、NOP、NOP 、NOP 、ACTIVE、NOP 、autdone=1和autdone=0。单个写功能由start_sig=3’b001发起的,之后就是按照13个状态按顺序进行。autdone=1和autdone=0两个状态产生一个正脉冲表示写动作完成了。最后当start_sig=3’b000时返回IDLE状态。

逻辑控制部分

逻辑控制部分是一个重要的部分,是整个控制器的控制中心。逻辑控制部分主要功能如图12逻辑控制部分流程图所示。

逻辑控制部分在上电复位时

- μClinux下SDRAM数据交换区的生成和使用(06-04)

- 基于DSP的数码望远相机的研究与设计(03-28)

- DSP片外高速海量SDRAM存储系统设计(01-18)

- 基于DSP片外高速海置SDRAM存储系统设计(03-12)

- DSP片外高速海置SDRAM存储系统设计方案(06-13)

- FPGA最小系统之:最小系统的概念(06-05)