基于CPLD的DRAM控制器设计方法

需要MUX、UCAS和LCAS。

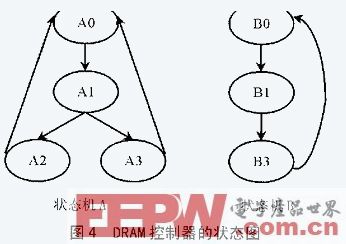

在T3的上升沿,状态机A等待状态机B中断此序列。如果MUX有效(DRAM读或写),它将保持有效。

有下一个降沿,状态机B采样总线状态信号。如果状态信号仍然有效,则此状态为等待状态Tw,状态机B保持在状态B1。如果这个状态是等待状态,并且RAS有效(DRAM访问),RAS保持有效;如果状态为等待状态,并且UCAS和LCAS有效(DRAM读或写),UCAS和LCAS保持有效。

在等待状态的上升沿,状态机A继续等待状态机B来中断此序列。如果MUX有效(DRAM读或写),则它在T3状态里保持有效。

如果微处理器状态信号无效,这个状态则是一个T4状态,状态机B从B1转到B2.如果状态是一个T4状态,并且RAS有效(DRAM访问),则 RAST4状态,并且RAS有效(DRAM访问),则RAS逻辑也检测无效状态信号,并且XC95C36关闭RAS信号;如果状态是一个T4状态,并且 UCAS和LCAS有效(DRAM读或写),则CAS逻辑也采样总线状态信号;如果状态信号无效,则XC95C36关闭UCAS和LCAS信号。

在T4的上升沿,状态机A采样状态机B的状态。在状态机B处于B2状态的情况下,状态机A从A2状态(DRAM访问)或A3状态(存储器读或写,但不是DRAM访问)转到A0。如果MUX有效,MUX逻辑检查RAS的状态;如果RAS无效(指示一个终止周期),XC95C36关闭MUX。

在下一个CLKOUT下降沿,状态机B无条件地从状态B2转到B0,终止DRAM序列。控制转移给状态机A。

三、80C186XL RCU单元的编程

要使DRAM正常工作,就必须对80C186XL中与DRAM刷新有关的寄存器进行正确编程。这些寄存器包括:刷新时钟间隔寄存器(RFTIME寄存器)、刷新基地址寄存器(RFBASE寄存器)和刷新控制寄存器(RFCON寄存器)。

刷新时钟间隔寄存器(RFTIME寄存器)的编程公式为:Trefresh×fcpu/(Rrow+Rrows×补偿因子)。V53C8258 的技术参数规定,其刷新周期Trefresh为8ms,存储阵列行数Rrows为512。考虑到RCU取得总线控制权的延时,补偿因子取0.05。因此,微处理器在fcpu=20MHz工作频率下,RFTIME寄存器的取值为:0.008×20×10 6/(512+512×0.05),约为297.

刷新基地址寄存器(RFBASE寄存器)的编程。该寄存器的高7位,规定了DRAM容量大小。系统使用两片V53C8258情况下,RFBASE的取值为00H,DRAM占用微处理器的存储空间的00000H~7FFFFH(512KB)。

最后通过将刷新控制寄存器(RFCON寄存器)的REN位置位,来启动刷新控制单元。

若使用80C186XL的节电模式,则要求重新编程这些值。在写节电控制寄存器前,必须先用要时钟分频值去除原先设置在刷新间隔寄存器的值,来重新设置寄存器。

四、结束语

现在DRAM、CPLD的价格非常低,这样设计者有机会在嵌入式计算机系统设计中考虑采用DRAM。80C186XL嵌入式微处理器广泛应用于嵌入式计算机、程控通信和工业控制系统中,具有良好的性价比,其性能和功能是80C31、80C196等单片机无法比拟的,并能充分利用大量的PC平台软件。本解决方案已在家庭电子证券产品中采用,获得了良好的经济效益和社会效益。

掌握CPLD技术和VHDL语言设计技巧是提升产品技术含量的重要途径。上述CPLD还留在一些引脚和内部资源未使用,只要设计者将VHDL源代码稍微作一些修改,就可以用这些引脚控制新增加的DRAM,提供总线准备输出信号或DMA响应信号。

如果采用引脚数和宏单元较多的XC9672或XC95108CPLD,就可以将D触发器(74HC74)、多路地址切换器(74HC157)、数据收发器(74HC245)和地址总线锁存器(74HC373)等其它分立逻辑器件的功能全部集成到CPLD中,这样系统集成度和可靠性将更加提高。

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)