基于2.5 Gbps收发器的相位锁定检测电路设计与仿真

时间:07-04

来源:电子产品世界

点击:

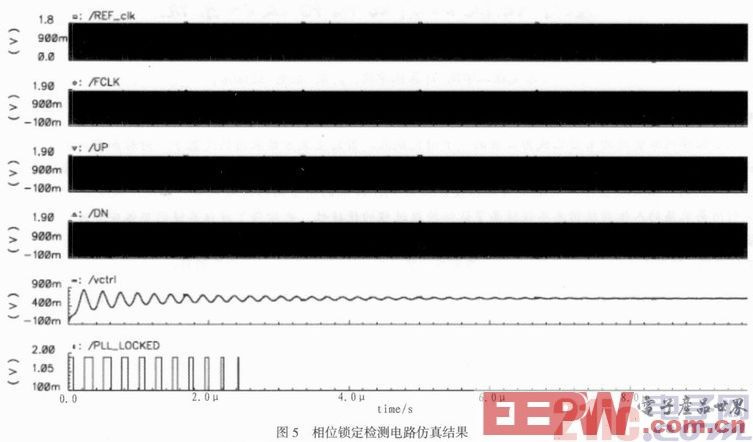

为验证电路的功能性能是否符合要求,采用smic0.18μmCMOS工艺完成电路设计后,在cadence的spectre上进行仿真,仿真结果如图5所示。从图中可以看出当输入时钟和反馈时钟同相以后,需要等待218个时钟周期后会输出有效锁定信号,整体闭环仿真中控制电压逐渐稳定,锁相环进入动态平衡。

3 结论

文中描述了锁相环的关键电路,相位锁定检测电路的设计与仿真,通过分析常用的相位锁定检测方法,根据设计实际提出了一种全定制的数字实现方案,可以实现1/18时钟周期的精度检测,保证了电路的可靠稳定工作,采用SMIC0.18μm CMOS混合信号工艺完成了电路的设计、仿真,结果表明该电路在2.5 Gbps时钟数据恢复电路中可以稳定可靠地工作。

- 锁相环控制及初始化简析(08-27)

- 单片机最小系统组成及电源/复位/振荡电路解析(01-03)

- FPGA系统设计原则和技巧之:FPGA系统设计的3种常用IP模块(06-05)

- 基于VHDL的感应加热电源数字移相触发器设计(06-05)

- 针对FPGA优化的高分辨率时间数字转换阵列电路(06-05)

- 基于DSP的软件锁相环的实现(02-06)