基于三相可控硅的半控桥数字触发器设计

时间:08-18

来源:互联网

点击:

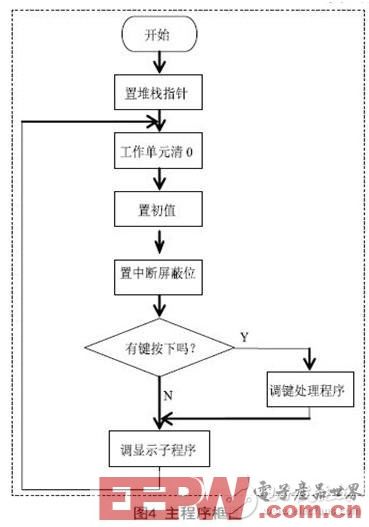

堆栈指针设计、清工作单元、设置初始值、开放中断、键盘扫描等的初始化工作,框图如图4所示。

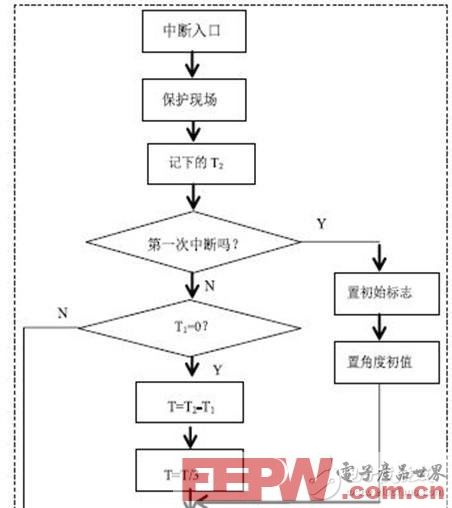

2.同步电压中断子程序。当同步电压由正半波到负半波过零时刻产生一个尖脉冲,加到单片机的EXTINT端引发外部中断。

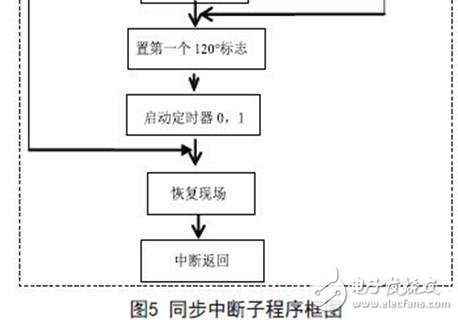

在中断服务子程序中完成置角度初值,测量及计算电源电压周期,设置第一个时间间隔,启动软件定时器0和定时器1.软件定时器0中断处理子程序。控制角α用一个软件定时器产生定时时刻来获得。当同步脉冲出现后,此即为A相的自然换相点(即A相α=0的时刻),此时将与控制角对应的时刻置入软件定时器0.当软件定时器到时后,一方面发出A相的触发脉冲,另一方面又将T/3时刻置入软件定时器0;当软件定时器到时,一方面发出B相的触发脉冲,另一方面又将T/3 时刻置入软件定时器0;当软件定时器到时,发出C相的触发脉冲,此时不可再将T/3时刻置入软件定时器0.很明显,当给定电压固定时,A、B、C三相的触发脉冲一定是相差T/3的,所以在A相的同步脉冲出现后,将αt置入软件定时器0,软件定时器0到时时刻所就是所需的A相脉冲的控制角α。在子程序中完成给定电压与反馈电压的采样,控制角α计算,标度变换以及将控制角度数值送到显示缓冲区等工作。程序框图略。图5是同步中断子程序框图。

采用16位单片机80C196KC系统,器件减少、结构紧凑,整个触发器电路大为简化,并且,由于单片机运算速度快,采样与显示可以在两次同步信号之间完成而且每次同步信号都被采样,因而中断程序可以按照最新的采样数据调整触发脉冲的移相角。实验表明,该触发器的动态特性好、控制精度高。

- 基于DSP的晶闸管数字触发器的研究与设计(01-20)

- 基于VHDL的感应加热电源数字移相触发器设计方案(03-20)

- 复位设计中出现的结构性缺陷及解决方案(04-30)

- Verilog HDL基础之:时序逻辑电路(06-05)

- FPGA设计频率计算方法(06-04)

- 简单的JK触发器的VHDL程序(11-30)