一种基于FPGA的全光纤电流互感器控制电路设计

为200 kHz左右,为保证该方波信号无失真通过后端滤波电路,滤波电路的高频截止频率必须以不损失20倍的方波基频信号的谐波设计,同时为避免高频噪声进入后端采样量化模块,高频截止带宽不能太宽,本设计中采用4 MHz带宽的π型滤波器实现前端滤波。

2.2 数据采集电路

为保证0.2S级(即千分之二)测量准确度,A/D转换位数需要达到10位以上。此外,为保证对200 kHz方波信号每个周期高低电平采样次数,从而可以通过累加求平均来提高采样精度,需要在每个周期内方波高低电平分别进行20次以上采样后求平均,这就要求模数转换器采样率大于8 MS/s.设计中保留一定余量采用量化位数14位、采样率20 MS/s的模数转换器 AD9248.该芯片采用多级的带有输出错误纠正逻辑的差分流水线结构,集成了两个高性能采样保持放大器和一个基准电压源,只需要提供控制时钟,其转换数据在7个时钟之后自动出现在数据端口,用于精密时序控制场合非常方便。

2.3 FPGA控制电路

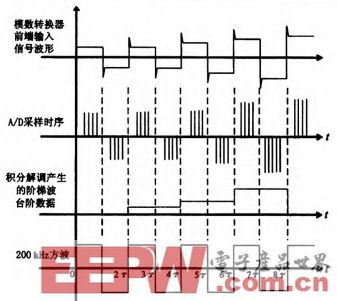

FPGA是光纤电流互感器控制电路实现信号检测与闭环控制的核心。如图1所示,其主要功能是负责生成整个控制系统的控制时序;完成A/D采集控制及数据读取、存储;对采集到的数字信号按预定的解调和积分算法进行处理,将处理后的数据在发送到阶梯波生成算法的同时,经滤波处理之后传到UART串口控制模块,完成与计算机的数据通信;此外还要将阶梯波生成算法产生的数据与方波数据叠加后控制D/A转换器输出相应的模拟信号。FPGA控制时序如图2所示,电路上电复位后, FPGA程序加载并对外围A/D、D/A及其他程控电路及接口初始化;FPGA内部时序控制模块产生周期5 μs的调制方波,该调制方波通过D/A控制接口输出到D/A产生同样周期的模拟方波信号并控制后端光调制器上产生±π/2的相移,确保前端光纤传感部分的相位检测灵敏度最高;模数转换器前端输入信号是含有相位差信息的交流信号,该信号的高低电平差值与相位差成正比,通过检测该信号的高低电平差值就可以间接获得当前相位差值,从而根据前面所述理论获得对应电流大小,该信号周期与方波周期一致。

FPGA通过时序控制单元控制A/D转换器在每个方波周期内对该信号高电平和低电平分别进行多次采样求平均后相减,获得该信号的解调信息即相位信息。由于前端光纤传感部分的相位差为0时表明实现一次闭环控制,因此,上述解调出的相位信息需要经过阶梯波生成算法将相位差信息转换为阶梯波台阶数据,再经过后端200 kHz固定方波和数字阶梯波叠加生成模块将该台阶数据与方波数据累加输出到D/A转换器,D/A转换器输出模拟信号驱动控制相位调制器产生抵消上述检测到的相位差信息,形成一次闭环控制。该处设计时应设计阶梯波累加判别程序,当阶梯波累加数据值超过驱动相位调制器产生2π相移时,应该减去相位调制器产生2π相移所对应值后再累加。由于该阶梯波台阶的高度反映了被测电流引起的相位差值,所以该值与被测电流也成线性关系,可将该值经数字平滑滤波后由FPGA内部设计的UART通信接口传输到上层控制界面用于计算当前被测电流的大小。

图2 FPGA闭环控制时序图

2.4 数模转换及驱动电路

该部分功能是把200 kHz固定方波和数字阶梯波叠加生成模块所输出的数字信号转变为模拟电压信号,经过功率驱动部分的放大和幅度调节控制相位调制器(在D/A满量程输出时,产生的模拟电压值为相位控制器半波电压的两倍),从而在光纤传感环中产生一个附加的反馈相移,抵消掉本次闭环控制周期内检测到的相位差。D/A选择主要考虑模拟信号输出建立时间、增益误差、输出线性度以及分辨率几个指标。D/A输出信号建立时间不仅对闭环控制带宽具有重要影响,而且当其建立时间较长时,会对输出阶梯波台阶的前、后沿影响很大,导致模数转换器前端输入信号的尖峰脉冲拉长,而有效采样时间窗口变短,因此建立时间越短越好。D/A的增益误差和输出线性度决定了输出模拟信号的误差和线性度,而模拟信号的误差和线性度施加在相位调制器上后或直接影响反馈相位的控制误差,因此需选择增益误差和输出线性度小的模数转换器。D/A的分辨率直接决定相位控制的最小分辨精度,其分辨率最好大于A/D的分辨率。设计中采用16位的高速D/A芯片AD9726实现该模数转换功能。由于该芯片为电流型输出,所以后端采用高速运放AD81l实现电流输出转电压输出和电压幅度放大功能。

3 实验验证及讨论

为验证上述控制电路性能,结合前端光纤电流传感头模块搭建了全光纤电流互感器装置。同时,采用大电流发生器(交流,有效值0 ~ 5 000A,50 Hz)作为测试电流源,并以

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)