基于VIM的嵌入式存储控制器的研究与实现

迟等待时间,由DRAM模块速度和延迟参数确定。从c_ACTIVE到c_WRITE或c_READ状态之间的虚线表示,在激活延迟小于1个时钟周期的情况下,DRAM从激活状态直接转换到读/写操作状态,延迟实际上隐藏在状态转换的时钟周期中。

3.4 刷新周期

DRAM存储器需要进行定时刷新,刷新周期描述如下:

(1)刷新模块每经过1个刷新请求周期,向控制模块发出刷新请求信号sys_REF_REQ;

(2)存储控制器的控制模块发出应答信号sys_REFACK对请求信号进行确认;

(3)应答信号在整个刷新阶段有效,sys_REF_REQ信号发出后必须得到sys_REF_ACK的确认,否则一直保持为高;

(4)在sys_REF_ACK有效期间,不能允许进行读写访问,直到刷新周期完毕,在刷新期间系统接口所有命令将被忽略;

(5)接收刷新请求后,命令状态机经过c_AR刷新状态-c_tRFC刷新等待状态-c_idle空闲状态的转换过程完成对DRAM的刷新控制。并等待接收系统访存指令,完成下一轮的读/写周期。

3.5 时序控制

时序控制是存储控制器实现中的关键部件,在VIM-1嵌入式存储控制器中用1个计时器子模块来实现对存控内状态机的时序控制。计时器子模块中包括1个时钟周期数锁存器ClkCNT和1个计时复位信号Reset_ClkCNT,具体时序控制描述如下:

(1)锁存器ClkCNT按时钟周期递增,每时钟周期ClkCNT的值加1,直到Reset_ClkCNT复位信号置1,ClkCNT清0;

(2)状态机转换到某个需要延迟操作的状态时,Reset ClkCNT复位信号置1,此时CIkCNT清0;

(3)状态机进入延迟等待状态,同时将Reset_ClkCNT复位信号置0,计时器从0开始计数,ClkCNT按时钟周期递增1;

(4)ClkCNT值到达指定延迟时间,相关状态机子模块控制状态发生转换,同时将Reset_ClkCNT置1,ClkCNT清0,进入下一个状态的时序控制。

4 功能模拟及综合验证

4.1 存储控制器功能模拟

在modelsim 5.7中对VIM-1嵌入式存储器进行了功能模拟,下面分别给出读写访问功能模拟结果。图5为存储控制器写周期时序波形图。该时序波形图反映了存储控制器将数据总线上的数据00000009H(H表示16进制)写入DRAM的过程。从图5中可以看到存储控制器在状态机cstate处于0110状态时240 ns,将数据送到输出数据线sdr_odq上,数据值为00000009H;完成数据的写入后,状态机转到写恢复状态0111(260 ns),经过两个周期后在280 ns回到空闲状态0000,写周期完成。

图6为存储控制器读周期时序波形图。同写周期时序波形图一样,图中正确反映了命令状态机在检测到控制总线上读命令后的状态转换过程,状态转换之间的延迟周期,每种状态所对应的DRAM命令信号,系统地址和数据总线上的值,DRAM地址线和数据线上的值。通过一系列的状态转换,在状态机cstate转换到1010数据输出状态(350 ns)时,存储控制器将前面存入DRAM存储单元中的数据00000009H,读取出来并传送到系统数据总线sys_odata上。

4.2 FPGA综合验证

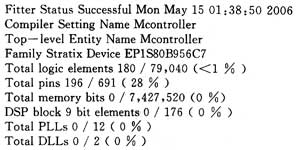

在QuartusⅡ环境中采用Altera的Stratix FPGA系列中的EPlS80对VIM-1嵌入式存储控制器进行了综合,下面是存储控制器综合结果。

5 结语

在PIM中嵌入向量处理逻辑的VIM系统结构,能充分发挥PIM高带宽、低延迟、低功耗的特点,可以有效解决存储性能瓶颈问题。基于VIM的嵌入式存储控制器是VIM系统的方存控制部件,是影响系统性能的发挥的关键,本文实现的VIM-1嵌入式存储控制器支持多种读写模式,具有严格的时序控制,每个存储控制器对应单独的存储模块,和VIM的存储交叉开关接口,使得多个方存部件可以同时访问多个存储体,具有较强的研究和应用价值。

- 在VIM中实现对嵌入式软件的调试(08-06)

- 基于ARM的新型智能交通信号灯系统设计(07-05)

- 在VIM中的嵌入式软件调试(02-25)

- Linux下vim编辑器的使用小技巧(08-16)

- 配置vim在源码中自动添加作者信息(07-31)

- VIM编辑器学习方法介绍(05-12)