基于VIM的嵌入式存储控制器的研究与实现

的地址分解成Bank地址、行地址和列地址,在特定的时候传输到DRAM地址线上;以及控制数据总线和DRAM数据线的数据输入输出。

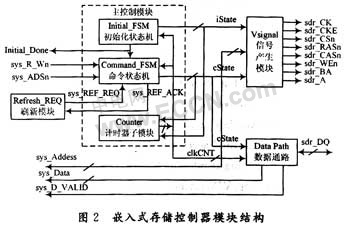

实现VIM-1嵌入式存储控制器,图2所示为其模块结构,存储控制器由主控制模块、信号产生模块、刷新模块和数据通路构成。

下面具体对每个模块的功能进行阐述:

3.1.1 主控制模块

主控制模块实现对DRAM各种功能的控制,由初始化状态机子模块、命令状态机子模块和计数器子模块构成。

初始化状态机子模块 在计时子模块的时序控制下,产生DRAM初始化过程中所需的各种状态,通过状态转换控制DRAM模块的初始化,并将其状态信号iState同时传送到命令状态机子模块、信号产生模块、计时器子模块和数据通路中。

命令状态机子模块 在计时子模块的时序控制下,产生DRAM读写周期和刷新周期过程中所需的各种状态,控制对DRAM模块的读写访问及刷新操作,并将其状态信号cState传送到数据通路模块、计时器子模块和信号产生模块中。

计时器子模块 根据DRAM模块的时序标准,对DRAM模块内部操作进行时序控制,主要通过控制初始化状态机和命令状态机中的状态转化时序,达到控制DRAM内部操作时序的目的。

3.1.2 刷新模块

产生对DRAM模块的刷新请求操作:通过内部的计数器控制,每隔一定的时钟周期(具体时钟周期数按照DRAM模块参数而定)向命令状态机发送刷新请求,直到命令状态机回复刷新请求应答。

3.1.3 信号产生模块

信号产生模块将初始化状态机发送的状态iState、命令状态发送的状态cState转换成DRAM所对应的内部命令信号,主要包括sdr_CKE(时钟使能信号)、sdr_CSn(片选信号)、sdr_RASn(行选信号)、sdr_CASn(列选信号)、sdr_WEn(读写信号)。同时在规定的时序下,将地址总线上传输过来的地址信号转换成DRAM内部所对应的Bank地址和行列地址。

3.1.4 数据通路

数据通路模块主要功能是在计时器子模块的时序控制下,根据命令状态信号,在相应状态时将数据总线上的数据写入DRAM存储体;以及将DRAM数据线sdr_DQ上的数据输出到系统总线上,同时在数据输出的过程中将数据有效信号sys_D_Valid置1。

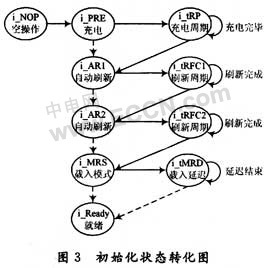

3.2 DRAM初始化

通常在DRAM正常工作,能够执行存储访问前,需要对DRAM进行初始化。主控制模块中的初始化状态机子模块实现对DRAM的初始化操作。如图3所示。

图3为初始化状态机状态转换图,初始化过程如下:系统复位时,DRAM空操作,初始化状态机处于i_NOP状态,系统复位完成且电源和时钟处于稳定状态时,DRAM初始化序列开始执行,经1次充电、2次刷新和载入工作模式操作,最后进入就绪状态,初始化序列完成。

初始化状态机中的载入模式状态启动DRAM内部载人工作模式命令,将地址总线上的数据加载到DRAM的模式寄存器中,配置用户所需要的工作模式。模式寄存器的内容定义了猝发长度、猝发类型及CAS延迟等,只要DRAM模块处于空操作状态,模式寄存器可以载入不同的值,继而改变DRAM的工作模式。

另外,由于DRAM的延迟周期根据实际DRAM速度级别的不同而不同,在延迟状态中等待的时钟周期数与时钟周期tCK相关,当时钟周期tCK大于延迟时间时(这里延迟时间指:充电周期、刷新周期和载入延迟),实际上就不需要等待,在初始化过程中,充电、刷新和载入工作模式到最后就绪状态之间的转换为图3中虚线表示的转换过程。

3.3 读写周期

图4为VIM-1嵌入式存储控制器命令状态机状态转换图,通过状态转换控制对DRAM的读、写访问和刷新操作。

系统复位时,DRAM空操作,命令状态机处于空闲状态,DRAM初始化完成后,命令状态机对总线地址选通信号sys_ADSn(低电平有效,表示总线请求)和刷新请求信号sys_REF_REQ进行检测,如果有刷新请求,那么命令状态机模块控制DRAM进入刷新周期,否则,若总线地址选通信号sys_ADSn有效,命令状态机转入激活状态,则DRAM进入读写周期。

命令状态机从激活状态无条件转入激活延迟状态,在激活延迟状态对系统控制总线上的读写命令信号进行检测,若信号为高电平(表示读访问)则命令状态机转入读操作状态,继而进行对DRAM读取数据操作;否则状态机转人写操作状态,执行写访问。

对DRAM一个完整的读访问周期需要经过的状态转换过程为空闲-激活-激活延迟-读操作-CAS延迟-数据输出,最后回到空闲状态。而对DRAM一个完整的写访问周期则需要经过空闲-激活-激活延迟-写操作-数据写入-写恢复-空闲的状态转换过程。

在所实现的VIM-1嵌入式存储控制器中,将DRAM地址位A[10]恒置高电平,设置为自动充电模式,所以对DRAM的充电隐藏在DRAM读写命令操作中。命令状态机转换过程中所涉及到的延

- 在VIM中实现对嵌入式软件的调试(08-06)

- 基于ARM的新型智能交通信号灯系统设计(07-05)

- 在VIM中的嵌入式软件调试(02-25)

- Linux下vim编辑器的使用小技巧(08-16)

- 配置vim在源码中自动添加作者信息(07-31)

- VIM编辑器学习方法介绍(05-12)