基于VerilogHDL的FIR数字滤波器设计与仿真

时间:01-06

来源:互联网

点击:

级文件, 并且调用了QuartusII 中的MegaFunction 功能辅助完成整个设计。

3、验证仿真

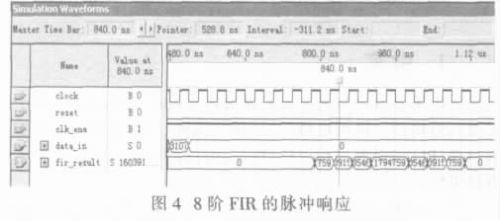

完全可综合设计的一个优点就是同样的HDL 代码能够用于验证和综合。在使用HDL 代码之前必须要验证设计的功能,最好且最简单的方法就是利用验证工具, 其次是利用仿真工具作有目的的仿真。QuartusII 内部带有仿真器, 只要通过建立正确的Vector Waveform File( 向量波形文件) 就可以开始仿真了。图4 所示为QuartusII 内部仿真器得到的8 阶FIR 的脉冲响应波形。

3 结论

利用Verilog HDL 设计数字滤波器的最大优点就是可使设计更加灵活。比较硬件电路图设计, Verilog HDL 语言设计的参数可以很容易在Verilog 程序中更改, 通过综合工具的简化和综合即可以得到电路图, 其效率要高出利用卡诺图进行人工设计许多。而且编译过程也非常简单高效。优秀编码风格能够在综合过程中节省芯片使用的单元, 从而降低设计成本。

- 基于SystemC 的系统验证研究和应用(08-10)

- SoC:IP是新的抽象(10-24)

- 从传统电路检查到先进可靠性验证的最佳实践(07-03)

- 基于Verilog语言的等精度频率计设计(08-14)

- Verilog串口通讯设计(06-06)

- Verilog HDL 设计模拟(06-06)