采用C/C++、OpenCL编程中的下个逻辑步骤

境 (IDE)。利用 该环境,开发人员可以创建针对不同数据中心应用 可即时换入换出而优化的动态重配置加速器 , 可即时 换入换出。开发人员可使用该环境创建诸多应用, 这些应用能在运行时间内将众多内核换入和换出 FPGA,且不会干扰服务器 CPU 与 FPGA 之间的接 口连接,从而实现不间断的应用加速。SDAccel 环 境针对的是基于 x86 服务器处理器的主机系统,并 提供现成商用插电式 PCIe 卡,以增加 FPGA 功能。

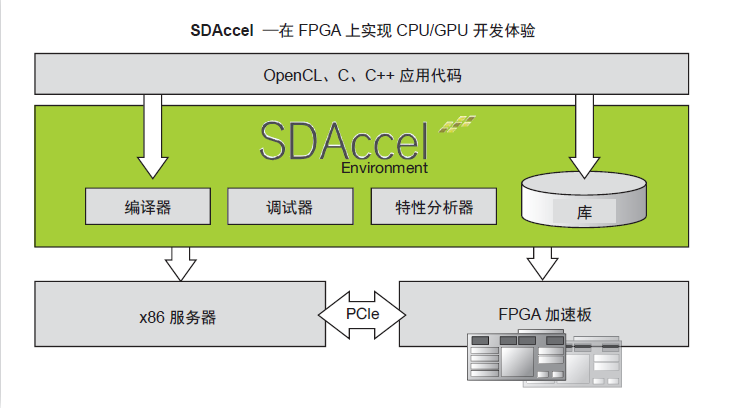

图 2 - 面向 OpenCL、C 和 C++ 的 SDAccel 开发环境可将单位功耗性能提高 25 倍,利用 FPGA 实现数据中心应用加速。

凭借 SDAccel 环境,开发人员即使先前没有 FPGA 经验也能使用 SDAccel 似曾相识的工作流程 来优化他们的应用,并充分发挥 FPGA 平台作用。该 IDE 提供编码模板和软件库,并可用来针对所有开发目标进行编译、调试和特性分析,包括 x86 上 的仿真、使用快速仿真进行性能验证,以及 FPGA 处理器上本地执行。该开发环境在面向数据中心的 FPGA 平台上执行应用,而且能自动插入工具以实现 所有开发目标。赛灵思设计的 SDAccel 环境能够让 CPU 和 GPU 开发人员轻松将应用迁移到 FPGA 上, 同时在熟悉的工作流程中维护和重用 OpenCLTM、C 和 C++ 代码。

SDAccel 库对于 SDAccel 环境能实现类似于 CPU/GPU 的开发体验起到了重大作用。SDAccel 库 包含低级数学库以及生产力更高的库(如 BLAS、 OpenCV 和 DSP 库)。这些库用 C++(而非 RTL) 编写而成,因此开发人员可在所有开发和调试阶段完全按所编写的内容来使用它们。在项目早期,所有开发工作都在 CPU 主机上完成。因为 SDAccel 库 用 C++ 编写,所以它们能够与 CPU 目标(创建一个 虚拟原型)的应用代码一起编译,从而允许所有测 试、调试和初始特性分析在主机上进行。这个阶段 无需 FPGA。

SDSOC 支持 ZYNQ SOC 和 MPSOC 系统的嵌入式 开发

赛灵思为嵌入式系统开发人员设计了 SDSoC 开发环 境,用以针对赛灵思 Zynq SoC 和即将推出的 Zynq UltraScale+ MPSoC 进行编程。SDSoC 环境提供极 大简化的嵌入式 C/C++ 应用编程体验,包括一个可 在裸机或操作系统(例如 Linux 和 FreeRTOS)上运行的简单易用的 Eclipse IDE。该环境是一种用于异构 Zynq SoC 和 Zynq MPSoC 平台部署的综合而全面 的开发平台(图 3)。SDSoC 环境还配套提供业界 首款 C/C++ 全系统优化编译器,支持系统级特性分 析、可编程逻辑中的自动软件加速、自动系统连接 生成,以及可加快编程速度的多种库。该环境还为 客户和第三方平台开发人员提供开发流程,以使平 台能够在 SDSoC 开发环境中使用。

图 3 – SDSoC 开发环境提供熟悉的嵌入式 C/C++ 应用开发体验,包括简单易用的 Eclipse IDE和综合而全面的设计环境,以实现异构 Zynq All Programmable SoC 和 MPSoC 部署。

更多关于让您能够将代码性能最大化的文章,请点击“软件开发及嵌入式系统开发人员必备”

xilinx zynq poencl SDAccelTM 相关文章:

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序(07-15)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 利用NI CompactRIO与NI Single-Board RIO实现从快速构造原型到低成本发布(03-19)

- 创建还是购买:什么是您嵌入式设计的最好选择?(07-06)

- Pmod规范,或Arduino伪标准(08-27)