详解ARM Cortex-A32处理器 打造超高能效嵌入式环境

行指令组成,通常是特定异常处理器的分支指令。仅支持两种外部中断源,即FIQ和IRQ。通常,一个高优先级中断会连接FIQ,其他则连接IRQ。这意味着系统要么装有软件调度程序,要么就要和现代系统一样装有中断向量控制器(Vectored Interrupt Controller,VIC),可以利用单一向量地址进行编程。

多数Cortex-A系统装有基于ARM的通用中断控制器(Generic Interrupt Controller,GIC)。GIC是许多物理中断和ARM核心中断输入(FIQ和IRQ)的接口,处理优先次序、遮蔽、单一中断启用或禁止,及优先权。欲了解更多信息,请参考《GIC架构参考手册》。

虚拟内存支持

支持完全虚拟内存环境是ARMv8-A的一个主要特性,使设备可以支持Linux和Android等平台操作系统。同样,虚拟内存能力通常也是客户选择核心的重要依据。

虚拟内存环境使操作系统能够以更加灵活的方式管理内存,例如,允许单独处理动态扩展栈区域,按照需求将单个代码和数据区域调入和调出外部存储页面,并使每个用户处理系统内存映射的相同视图。

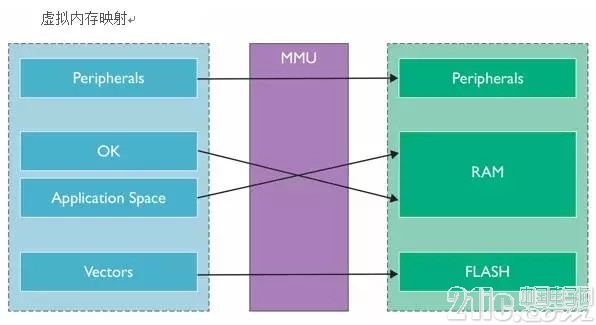

图6:虚拟内存

为此,如图6所示,虚拟内存在处理器提供的每个地址上进行“转换”。软件在“虚拟地址空间”和称为内存管理单元(Memory Management Unit,MMU)的模块中运行,并将其转换为“物理地址空间”,为系统中的每个用户任务以及操作系统本身创建新的虚拟内存映射,还使操作系统完全控制访问权限等。每项任务都可以在自身的虚拟内存空间中执行,就像是系统中的唯一任务。只有操作系统知道外部物理内存中该任务的代码和数据区域的真实物理位置。

任务切换时,操作系统的其中一项工作就是重新配置MMU,使代码和数据能被输入任务使用,同时让输出任务的存储器可以暂时访问。这进一步增强了任务之间的分离,构建安全可靠的系统。

这里我们不再深入研究所有细节。简而言之,ARM处理器的MMU使用了“页面表”(外部存储器中)的数据,驱动并控制转换。系统已经经过一系列优化(如转换查找缓冲器(TLBs),缓存通过转换降低读取页面表的功耗),让转换过程的功耗降到最低。

ARM Cortex-A32 处理器 嵌入式环境 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)