基于CPLD的LCD1602显示系统设计与实现

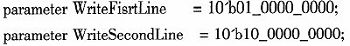

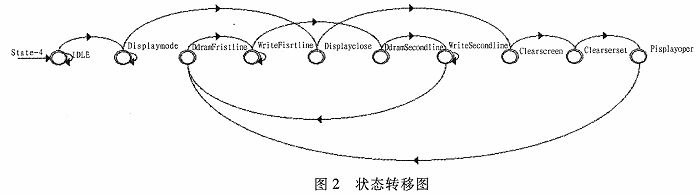

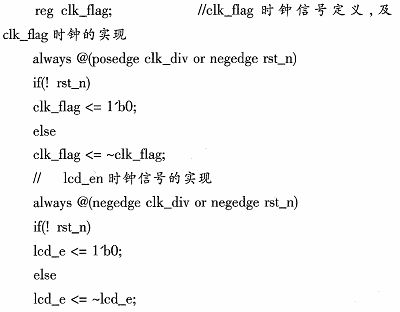

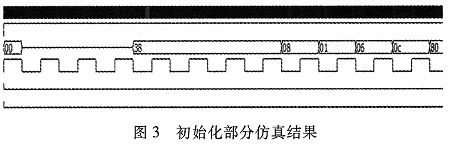

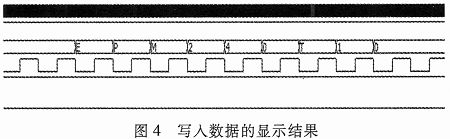

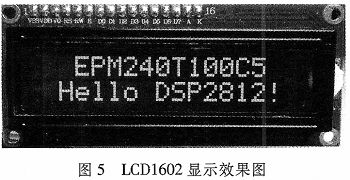

统。状态采用一位独热码进行编码。所定义状态如下: 在QuartusⅡ平台下,经综合所得的状态转移关系如图2所示。 要想实现状态的转移,需构建LCD1602显示模块所必需的时钟,在时序分析过程中已确定将E信号的周期设计为5ms,而数据的写入以及RS、R/W电平的变化总是在E信号低电平的中间发生,因此可重新建立一个时钟,使其在该位置发生跳变,可以是上升沿也可以是下降沿,其周期与E信号周期相等,为便于设计,也将该时钟设计成脉宽为50%的方波信号。这里设E信号的时钟为lcd_en,在E信号低电平中间位置跳变的时钟为clkjlag。若选择 clk_flag的上升沿触发RS、R/W电平的改变及数据的写入操作,则显然clk_flag高电平要超前clk_div高电平90°。为得到相位上互差90°的两个时钟,可以通过对系统时钟分频,构建一个周期为2.5ms的时钟clk_div,使得clk_flag总是在clk_div的上升沿翻转,而lcd_en总是在clk_div的下降沿翻转,由此即可得到相位上互差90°的两个时钟信号了。由于主时钟为30 Mhz,因此需对其进行37 500分频,即可得到周期为2.5 ms的clk _div。其软件实现如下: 由clk_div时钟信号获取lcd_en及lcd_flag两个时钟信号,具体如下: 至此,只需捕获clk_flag的上升沿,并在该跳变沿处送入指令或数据即可。而状态之间的转移关系则需按初始化的正确步骤进行,完成初始化后,指定DDRAM的地址,并向lcd_dat送数据即可实现数据的写入操作。 4 仿真结果及实现效果 软件仿真借助了第三方的仿真软件Modelsim,在QuartusII当中利用Test Bench Template Writer建立仿真模板文件,并在模板当中给出激励条件,编译后即可生成用于仿真测试的vt文件了。初始化部分的仿真结果如图3所示。 上图信号从上到下依次为:clk,rst_n,lcd_dat,lcd_en,lcd_rs,lcd_rw。由图3可知,由于系统时钟频率较高,clk已显示为一条粗线,rst_n仅延时10个仿真单位,即被拉高为高电平,lcd_dat中出线一段蓝色线条,占lcd_en的3个周期,即实现了15ms的延时,紧接着的四个周期连续写入8’h38,然后8’h01等,直到8’h0c完成对LCD1602的初始化。图4为初始化后向LCD1602写入的数据,由于显示内容的编码与ASCII码基本一致,可将其设置为ASCII进行观察。 将Verilog HDL编写的程序进行编译,并将生的目标代码下载至EPM240T100C5,最终显示的效果如图5所示。 5 结束语 通过对LCD1602时序进行详细分析,本文实现了用CPLD驱动LCD1602显示模块工作的目的。通过仿真及硬件验证,均说明了设计的合理性与正确性。另外,采用模块化设计,也为后续系统的大规模化和可扩展性提供了很大方便。相比单片机实现过程,利用CPLD实现显得更加简单、方便。另外,CPLD管脚的可配置特点也为CPLD的使用带来了极大的灵活性。随着CPLD及FPGA技术的发展,数字系统设计也必将发展到一个新的阶段。

LCD1602 显示系统 时序 Vetilog HDL 相关文章:

- 单片机定时器实现实时时钟程序-lcd1602显示(12-02)

- 单片机写LCD1602液晶程序源码(12-02)

- 单片机I2C通信及LCD1602显示C程序(12-02)

- 单片机LCD1602底层驱动子程序(12-02)

- 51单片机加HC—SR04超声波测距仪用LCD1602显示(12-02)

- PIC单片机驱动LCD1602液晶显示字符串程序(12-02)