基于DM368的视频捕获与编解码系统设计

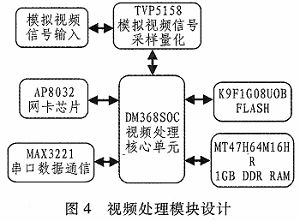

控制器,可以充分使用外部DDR2存储器。本次设计采用一片1G容量DDR2存储器,该RAM与DM368的内存引脚相连,为该芯片处理大数据视频提供了足够的运行空间。使用三星公司的1G容量FLASH作为Linux系统内核、文件系统和视频应用程序的存储区域。

在视频输出部分,DM368自带了模拟视频输出接口,另外考虑到嵌入式Linux的开发调试需求和目前常用的视频传输方法,本次设计还添加了网络和串口。网卡主控芯片采用

AR8032,串口部分采用MAX3221实现通信电平转换。整个视频处理模块硬件设计如图4所示。

3 系统软件设计

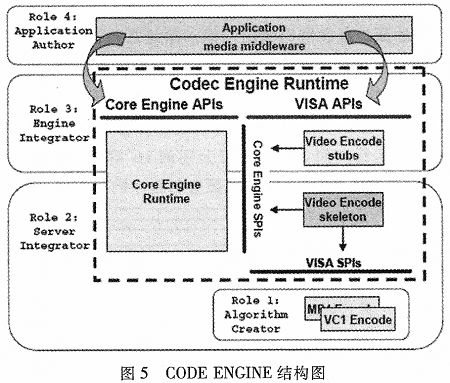

TI公司为达芬奇系列视频处理器设计了软件开发构架,方便开发者在这个构架上开发自己的视频处理程序。该软件开发构架核心为CODE ENGINE编程框架,它能够自动地请求和实现符合eXpress DSP的Codec算法。在code engine中为开发人员提供3种开发方向。作为算法开发人员,可以将设计好的视频处理算法通过Codec部分,按照TI通用的视频处理算法标准生成算法库,并进行打包。视频应用程序开发人员可以在APP部分调用已经打包好的算法库,开发自己的视频处理应用程序。在应用程序与算法库之间是sever部分,该部分可以实现Codec算法库被APP调用。Server为Codec提供APP调用过程中所必须的组件(例如BIOS、Framework Component、DSPLink等),并生成可执行文件[dv]。系统软件设

计的结构图如图5所示。

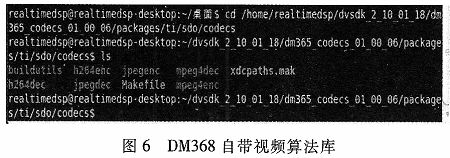

在本次视频编解码软件设计中,DM368自带了MPEG4和H.264视频编解码算法。在安装好的开发环境中,进入算法库文件夹,查找MPEG4视频压缩算法与解压算法。图中显示的库文件提供的是可以直接被APP端使用的,下一步就是编写相应的应用程序。

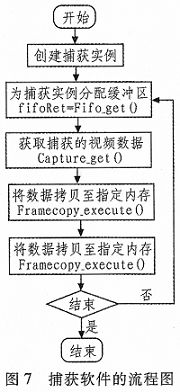

设计视频处理应用程序,主要需要编写Capture、encodedecode和display3个部分的代码。在Capture中主要使用前缀为 “Capture_”的函数,这些函数直接使用了V4L2的相应函数接口,从而帮助软件从底层获取与视频处理相关的数据。其主要执行流程如图所示。

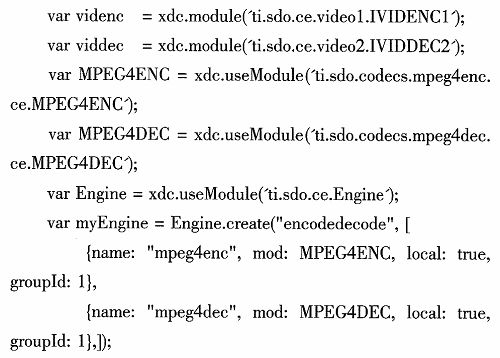

在视频编解码软件部分中,主要使用了DM368自带的视频编解码算法,在编程之前需要首先配置encodedecode.cfg文件。配置参数如下:

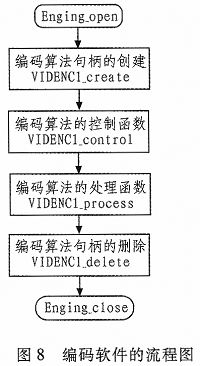

配置完成后,在应用程序中便可以创建编码算法句柄调用算法库。编码与解码都需要首先打开engine,然后创建算法句柄,接着操作算法控制函数与算法处理函数。最后执行完毕删除编码算法句柄,并关闭engine。以编码为例,流程图如图所示。

在Linux下实现视频输出程序display,是通过操作framebuffer实现的。该帧缓存提供了个多种操作方法。开发者想要在显示屏中显示视频其实就是将解压后的视频数据写入framebuffer中来完成的。至此视频处理应用程序编写完毕。

4 系统测试

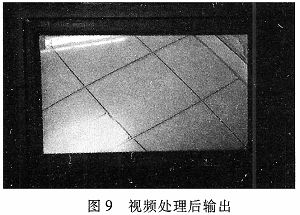

在Linux开发环境中打开终端,更改路径进入源代码文件夹:cd/dvsdk_2_10_01_18/drsdk_demos_2_10_00_17/dm365/encodedecode。输入 make,Makefile文件会自动编译整个工程。将编译好的整个文件夹复制到nfs共享路径下。使用串口与网线,将电路板与开发主机相连。最后连接显示器与模拟视频输出端口。上电之后更改当前路径到测试目录,首先加载该视频测试程序所需的驱动模块:./loadmodules_sd.sh。加载完成后打开运行测试程序./video可以看到编解码视频的输出情况,移动摄像头可以看到视频有明显延时。显示情况如图所示。

5 结论

经实验表明,该系统可以对摄像头采集到的模拟视频信号进行采样量化,并实现对原始视频数据MPEG4编解码的功能,最终将视频数据稳定输出到显示屏上。本次设计达到了预期的目标。DM368芯片功能比较全面,硬件设计相对更简便,又拥有丰富的软件资源和算法库支持,可以大大缩减相关视频处理项目的开发周期,并同时在很大程度上增强系统可靠性。该设计除此之外该系统还支持H.264编解码,可以通过网络接口和Linux运行平台进行网络传输。整个平台功能丰富可扩展性高,为其他视频处理设计提供了参考。

- DM368 视频前端信号采集详解(07-29)

- 一种MPEG4视频压缩和传输系统(10-29)

- 基于SOPC的MPEG4视频播放器(09-12)

- 在FPGA上实现H.264/AVC 视频编码标准(07-23)

- 用FPGA替代DSP实现实时视频处理(08-26)

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)