基于ARM的分布式干扰机控制单元设计

主从装置标志位并进行显示,若读到从机,则将FPGA中的信息显示到界面中;若为主机,直接读取FPGA延迟量更新标志位。若为更新,则表示FPGA有新信息,需要点击设置将当前界面更新为最新参数,然后开始重新计时。

3.4 运行测试

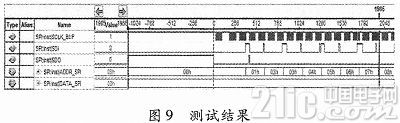

对设计好的分布式干扰机控制单元进行测试,按照与FPGA的通信协议,ARM界面信息转化为数据后,每8位一组,两组为一个信息单元进行传送。反之,当FPGA对ARM发送数据时同理对数据进行解析。利用FPGA的逻辑分析仪对发送与接收的数据进行采样,结果如下图9所示。

图9中,SCLK_BUF为时钟信号,每8个时钟脉冲为一个时钟周期;SDI为ARM发送的数据,SD0为ARM接收的数据;ADDR_SPI与DATA_SPI为ARM发送数据的低8位与高8位。从图中可以看出,ARM端发送的数据依次为00h,00h,01h,00h,02h,00h,03h,00h……。在FPGA一端,收到的数据同样是00h,00h,01h,00h,02h,00h,03h,00h……,其中ADDR_ SPI的数据就是收到数据的奇数项,其中DATA_SPI的数据就是收到数据的偶数项。同时,在第3个有效脉冲周期到达时,ARM控制单元接收到来自FPGA的数据,这个数据解析后反映到ARM界面即为装置属性选项,界面会自动响应将装置属性选项设置为主装置。

综上所述,表明ARM控制单元能够按需求向FPGA发送相应的数据,同时能够正确接收来自FPGA的数据并进行自动解析,实现了该分布式干扰机ARM控制单元的功能。

4 结束语

以友善之臂公司的Miero2440开发板及7寸触摸屏为平台,S3C2440为主控单元,开发了ARM的SPI驱动,设计了分布式干扰机的控制单元,并进一步优化了该控制单元的实用性。该控制单元具有成本低、功耗小、功能可扩展、适用性强、便于移植等特点,具有较好的通用性。

ARM 分布式干扰机 Fedora SPI Qt 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)