基于Xilinx V5的DDR2数据解析功能实现

四通道的脉冲个数,地址3h再为第一、二、三、四通道的脉冲周期…如此循环依次为脉冲周期、脉冲宽度和脉冲个数。

将图2所示的数据文件通过PCI桥芯片下发至FPGA,提供给底层模块使用。同时定义FPGA的复位寄存器和DDR2的工作寄存器,实现软件复位,完成DDR2的读写控制设置。两组DDR2控制子模块是调用的Xilinx的MIG IP核。配置如图3,由于含有两组DDR2,所以其中的Number of Controllers应选择2。

在完成DDR2的管脚定义后,需要参考DDR2的工作控制参考资料以实现DDR2的用户定义,完成相关部分的程序代码设计,其中app_af_cmd =3’h0时,DDR实现写的指令,app_af_cmd=3’h1时,DDR2实现读的指令。DDR2用到的时钟是固定的200 M时钟,此时同样需要用到晶振50 MHz时钟通过PLL倍频至200 MHz,以实现传输数据的有序控制,而不会产生时序上的混乱。

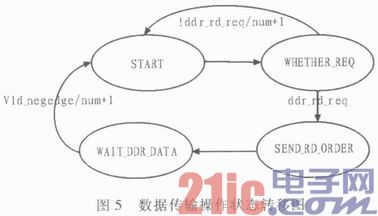

为了能够实现4个通道数据传输的互不干扰,可以在程序代码设计中使用状态机进行控制,部分程序代码如图4所示,相对应的数据传输操作状态转移如图5所示。同时只有正确接收到3个数据(脉冲周期、脉冲宽度、脉冲个数)时,脉冲才能正常的传输,所以需要用到两个寄存器,第1个寄存器作为缓冲器用来接收数据,当缓冲器接收完3个数据时,将其3个数据同时发送至第2个寄存器,以控制输出的脉冲波形。每接收到一个数据对其地址加1,以反过来读取下一个地址的数据。

3 系统验证结果与分析

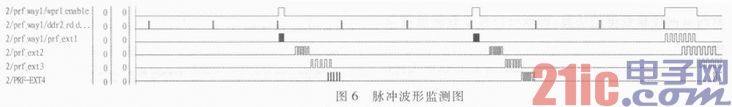

在系统验证的过程中,一旦系统接收到发送脉冲波形的命令后,就将数据文件解析成的脉冲波形通过DDR2发送,运用Xilinx自带的Chipscope对发送出的脉冲波形进行监测,结果如图6所示。

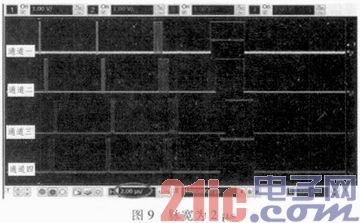

从图6中可以看出4个通道的前3个脉冲个数分别为5,6,7,和图2参数文件中数据的一致。通过SMA接口将波形连接到示波器上进行观测,示波器上对应的1,2,3,4分别为第一、二、三、四通道的波形图,观测到的波形如图7所示,和Chipscope上抓取的数据保持一致。为了进一步的验证结果的正确性与否,我们以通道一为例,对其进行解释,通过示波器引出波形,进一步验证脉冲波形的周期和脉宽。以参数文件的00000090h:07D0h=2000d为例计算周期,2 000/100 M=20 μs,如图8所示。以000000A0h:C8h=200d为例计算脉宽,200/100 M=2μs如图9所示。

观测图形可看出通道1的周期为图中箭头部分的距离,为5μs×4=20μs,结果正确。

观测图形可看出通道1的脉宽为图中箭头部分的距离,为2μs,结果正确。

4 结论

文中没计并完成了一种基于Xilinx V5的DDR2的数据解析功能的实现,了解了CPCI总线与FPGA之间的通信协议过程,同时根据外部数据文件实现了对输出的脉冲波形进行控制,检测到的信号波形也准确无误,有效的控制了发射时间,在雷达应用领域中具有一定的参考价值。

Xilinx Verilog DDR2 数据解析 信号波形 相关文章:

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序(07-15)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 利用NI CompactRIO与NI Single-Board RIO实现从快速构造原型到低成本发布(03-19)

- 创建还是购买:什么是您嵌入式设计的最好选择?(07-06)

- Pmod规范,或Arduino伪标准(08-27)