在KeyStone 器件实现IEEE1588 时钟方案

用KeyStone 外部的VCXO,因此从时间源上保证各个计时器之间没有累积误差。这样计算出来的各个绝对时间也是固定不变的。

关于同步信号的时间戳,有两点需要说明:

1. KeyStone 芯片的1588 功能不维护绝对时间戳,时间信息是从CPTS timer 或者PA 的timer 换算出来。这样也不支持对1588 报文发送时实时修改,所以在用KeyStone 芯片做时钟源时,芯片只支持two step 模式。

2. 输出时钟方案需使用KeyStone1 芯片上的定时器的输出。因为CPTS(或PA)上打时间戳的计数器和定时器使用的时钟虽然是同源,但是相位不同,产生的PPS 时钟时,需要软件参与校正两个计数器,并对记录相应的相位差。具体实现时,需要首先对CPTS(或PA)里面的计数器和选定的Timer64 计数器相差相位进行计算。软件首先操作CPTS(或PA)寄存器,触发一个CPTS 时间戳记录事件(或者发起一个读取PA 时间戳寄存器的命令),然后马上读取timer64 的值。考虑到cache 问题以及硬件总线上的竞争可能性,软件应在一个循环内多次执行这个操作,保证执行程序加载到 L1 cache 中,两个时钟之间的相位差应该可以通过循环几次获得的值平均得到。

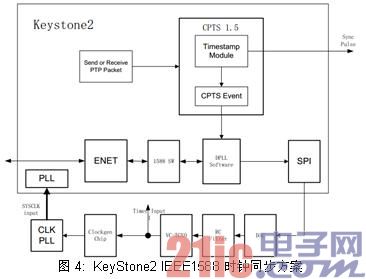

3.3 KeyStone2 1588 方案

KeyStone2 架构的TI 芯片对1588 的支持做了改进和增强。CPTS 模块支持同步以太网(Annex F)和1588 Annex D E 的报文。在KeyStone2 芯片中,PPS 输出是直接由CPTS逻辑驱动的。软件通过设置相关寄存器设置下一个PPS 输出时timestamp 的值,当计数器跑到设置的值的时候,硬件触发PPS 信号输出。

相比KeyStone1 的方案,KeyStone2 的主要优点在于:

1. 方案简单,涉及到的硬件和底层器件更少

KeyStone1 需要PA,CPTS,Timer64,QMSS 等外设和加速器来支持整套方案,而KeyStone2 只需要CPTS 一个模块就可以支持Annex D E 和Annex F 的PTP 报文,同时也支持同步信号的输出;

2. 时间戳个数减少,降低了计算复杂度

KeyStone1 里面需要计算包括PA 时间戳,CPTS 时间戳以及Timer64 的时间戳在内的共计3 个时间戳与PTP 报文的真实时间的绝对时间相差;KeyStone2 里面只有CPTS一个时间戳需要计算;

3. 方案全由硬件逻辑完成,彻底避免了软件干预同时也提高了同步精度

KeyStone 1 的方案由于记录时间戳的时间源(PA 和CPTS)与发送同步信号的时间源(Timer64)是不同的,因此在系统运行的时候需要软件计算不同时间源的绝对时间差,这样才能在后面的时间同步中精确调整时间。这里有软件读取并计算时间差的工作,这部分工作不可避免的存在软件误差,虽然可以通过多次计算取平均等统计手段缩小误差,但还是对精度存在一定的影响。KeyStone2 中,记录时间戳和发送同步脉冲都在CPTS中,因此无需计算两者的时间差,这样就避免了软件干预,也提高了同步精度。

4 KeyStone1 1588 方案实现

前文从原理和方案上描述了KeyStone 中如何实现1588 方案,本章节以KeyStone1 为例,从技术细节方面来阐述1588 实现方式。

以Annex F 的PTP 报文为例,1588 的实现主要分为配置Gbe Switch[3]和计算时间偏差两部分。整体流程如下:当接收(或发送)一个802.3 的PTP 报文时,Gbe Switch 会自动侦测到PTP 报文的接收(或发送)时间,并将该时间戳记录下来;用户根据记录下来的时间戳,配置Timer64 的时间输出信号,获取当前需要调整的时间偏差。

4.1 Gbe Switch 配置

KeyStone1 中的 Gbe Switch 是一个集成了1588 PTP 报文检测的交换机,其中CPTS 用来记录时间戳,CPSW 用来侦测1588 报文。因此1588 实现方式主要通过配置CPTS 和配置CPSW 来实现。

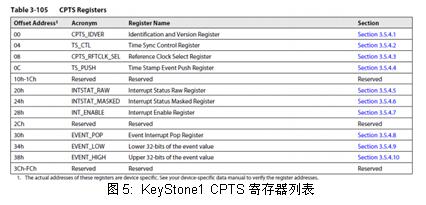

4.1.1 CPTS 配置

CPTS 是KeyStone1 架构中Gbe Switch 中的一个模块,请参考文献 [12] 中的2.3.5 章节。该章节详细介绍了CPTS 模块的工作场景和寄存器列表。

CPTS 配置步骤如下:

1) 复位CPTS 模块;

CPTS 的复位通过将TS_CONTROL 寄存器中的CPTS_EN 位域写0 来实现。

2) 选择CPTS 时钟源;

CPTS 时钟源在CPTS_RFTCLK_SEL 寄存器中选择,有四种时钟源可以选择:SYSCLK3,SYSCLK4,TIMI0 和TIMI1。其中SYSCLK3 是1/2 CPU 时钟,SYSCLK4是1/3 CPU 时钟,TIMI0 和TIMI1 分别是两个外部时钟输入pin 脚,原本是作为Timer64 的输入时钟,这里也可以复用为CPTS 的时钟源。

3) 使能CPTS 模块;

CPTS 的使能通过将TS_CONTROL 寄存器中的CPTS_EN 位域写1 来实现。当CPTS使能后,CPTS 内部的时间记数器就会根据输入时钟的频率开始记数。

4) 使能CPTS 中断;

CPTS 模块中断使能通过配置INT_EABLE 来完成。CPTS 可以产生多种事件的中断,主要有:

· Push 中断:用户手动触发一个 Push

- HyperLink编程和性能考量(01-15)

- 基于KeyStone 器件建立鲁棒性系统(10-29)

- 基于多核处理器的弹载嵌入式系统设计研究(02-18)

- Navigator Runtime 最大限度提高多内核效率(05-08)

- 基于KeyStone DSP的多核视频处理技术(09-15)

- KeyStone多核SoC工具套件: 单个平台满足所有需求(09-07)