基于AD9911频率源的设计与实现

式。AD9911初始化后,芯片默认进入单音模式并输出一个默认频率信号,AD9911接下来的工作模式由单片机从上位机接收的数据决定。软件设计中的不同功能模块均定义了相关函数来实现,单片机与上位机之间采用UART通信,单片机使用中断处理接收到的数据。

软件设计的重点在于写寄存器函数的编写,即使用PIC18LF4520的GPIO通过软件模拟出SPI串口。如图2所示,串行数据在SCLK上升沿写入,另外单片机和AD9911之间数据通信采用两线模式,CS为片选,所以定义单片机GPIO引脚RC3为串行数据输出SDO,RD0为控制时钟SCLK,RD1为片选信号CS。模拟SPI过程如下:首先拉低CS,在SCLK产生一个上升沿,SDO输出串行数据最高位bil7,然后拉低SCLK,串行数据左移一位,再拉高SCLK,SDO输出串行数据次高位bit6,如此重复8次即完成1 Byte的输出,传输过程中要注意端口状态建立和保持时间。

完成软件模拟SPI端口函数SPISim()后,写寄存器函数的编写采用若干次调用SPISim()的方式完成。单片机与上位机之间通信需要有相关的协议,单片机中断服务程序根据协议对接收的数据进行判断,从而完成相关的操作。本方案中,在拟发送数据前加了一个标志字节,单片机通过判断接收数据的第一个字节而进行相应的操作。

4 DAC重构滤波器设计

使用DDS产生低抖动时钟信号的主要挑战,在于降低DDS输出信号中存在的离散杂散成分所引起的确定性时间抖动。重构滤波器是从DDS产生干净的低抖动时钟信号的重要部件。重构滤波器用于在DAC的输出端衰减镜像频率。通常使用椭圆滤波器作为低通重构滤波器,与其他类型滤波器相比,在给定复杂度的情况下,椭圆滤波器可提供最快的通带至阻带转换。

理论上DDS的频率调谐范围可以从DC到系统时钟频率的一半,然而随着目标输出频率的升高,DDS输出频谱中第一个镜像频率将越来越接近目标频率。在实际操作中,将DDS输出频率限制为小于系统时钟频率的40%。这种做法既充分利用了DDS调谐带宽,又适应了外部滤波要求,降低了重构滤波器的复杂度并节省了成本。因此,设计重构滤波器截止频率为200 MHz。

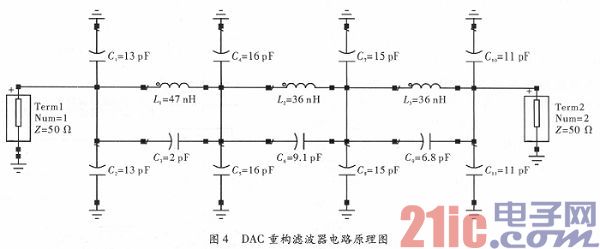

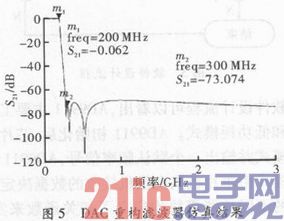

使用ADS软件自带集总参数滤波器设计向导完成椭圆低通滤波器设计,设计指标如下:通带频率200MHz;阻带频率300 MHz;通带衰减0.5 dB;阻带衰减70 dB;源和负载阻抗均为50 Ω。设计出满足指标的7阶椭圆低通滤波器,将设计软件综合出的元件值换为与之最接近的标准值,所得电路原理图如图4所示,仿真结果如图5所示。

如图4所示,S21曲线在200 MHz和300 MHz处的数值分别为-0.062 dB和-73.074 dB,满足设计指标要求。

5 测试结果

系统时钟频率fs=500 MHz,给定输出信号频率fo,则相应的频率控制字FTW可由式(1)计算得到。

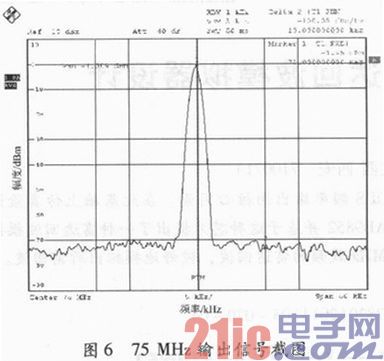

当fo=75 MHz,FTW=0x26_66_66_66。将FTW写入寄存器CTW0(0X04),使用罗德与施瓦茨频谱分析仪RS FSP40实测AD9911输出信号,结果如图6所示。从图中可以看出,输出信号相位噪声达到-100.08 dBe/Hz@10 kHz,且输出信号频率精确。

6 结束语

介绍了基于AD9911的频率源的实现方法,完成了使用PIC单片机控制DDS的频率源。通过利用单片机配置AD9911片内寄存器来实现对DDS芯片的控制,且在AD9911输出端设计重构滤波器以改善信号质量。实测结果表明,该方案输出信号相位噪声小、频率值精确,通过快速配置寄存器即可实现快速频率切换。

直接数字频率合成 AD9911 单片机 PIC18LF4520 频率源 相关文章:

- 基于FPGA的DDS IP核设计及仿真(06-05)

- 使用AD9850直接数字频率合成(DDS) IC (08-22)

- 基于MSP430F449的超低功耗高精度转达液位仪设计(07-09)

- 基于PIC18LF4520和AD9911的频率源设计(05-19)

- FPGA的DSP性能揭秘(06-16)

- 基于单片机通用引脚的软件UART设计(10-16)