ARM处理器结构

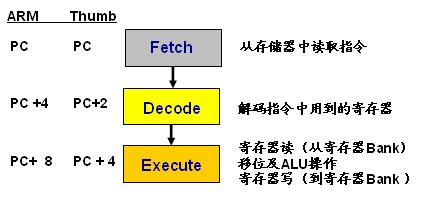

流水线模式下PC的更改过程

多周期ARM指令的3级流水线操作

数据路径涉及到所有执行周期、地址计算和数据传送。译码逻辑总是产生数据路径在下一个周期使用的控制信号,因此除译码周期以外,在STR地址计算周期也产生数据传送所需的控制信号。

取指的存储器访问和执行的数据路径占用都是不可同时共享的资源,对于多周期指令来说,如果指令复杂以至于不能在单个时钟周期内完成执行阶段,就会产生流水线阻塞。

ARM的流水线设计问题

1)缩短程序执行时间:

Tprog:执行一个程序所需时间;

Ninst:执行该程序的指令条数;

CPI:执行每条指令的平均时钟周期数;

Fclk:处理器的时钟频率。

措施:

提高时钟频率fclk(导致流水线的级数增加 )。

减少每条指令的平均时钟周期数CPI(需要解决流水线的相关问题 )

2)解决流水线相关:

结构相关:某些指令在流水线中重叠执行时,产生资源冲突 。

措施:1)采用分离式指令Cache和数据Cache。2)ALU中采用单独加法器来完成地址计算。

数据相关:当一条指令需要前面指令的执行结果,而这些指令均在流水线中重叠执行时,就可能引起流水线的数据相关。

数据相关有“写后读”、“写后写”和“读后写”等。

措施:1)旁路技术。2)流水线互锁技术。

控制相关:当流水线遇到分支指令和其他会改变PC值的指令时,就会发生控制相关。

措施:1)引入延时分支。2)尽早计算出分支转移成功时的PC值(即分支的目标地址)。

ARM的5级流水线

ARM9和StrongARM架构都采用了5级流水线.

增加了I-Cache和D-Cache,把存储器的取指与数据存取分开;

增加了数据写回的专门通路和寄存器;

把指令的执行过程分割为5部分:

取指:将指令从指令存储器中取出,放入指令流水线中。

指令译码:对指令进行译码,从寄存器堆中读取寄存器操作数。

执行:把一个操作数移位,产生ALU结果。如果指令是Load或Store,在ALU中计算存储器的地址。

数据缓存:如果需要,访问数据存储器;否则,ALU的结果只是简单地缓冲一个时钟周期,以便使所有指令具有同样地流水线流程。

写回 :将指令产生地结果写回到寄存器堆。

流水线对比

超标量执行

通过重复设置多套指令执行部件,同时处理并完成多条指令,实现并行操作,来达到提高处理速度的目的。

所有ARM内核,包括流行的ARM7、ARM9和ARM11等,都是单周期指令机。

ARM公司下一代处理器将是每周期能处理多重指令的超标量机。

超标量处理机:一个时钟周期内同时执行多条指令的处理机。

超标量处理器中的多指令单元

超标量与流水线技术是兼容的,为了能够在一个时钟周期内同时发射多条指令,超标量处理机必须有两条或两条以上能够同时工作的指令流水线。但与此同时,也带来了多流水线的调度问题和操作部件的资源冲突问题。

超标量处理器在执行的过程中必须动态地检查指令相关性。

如果代码中有分支指令,必须将分支被执行和分支不被执行这两种情况分开考虑。

计算执行时间几乎是不可能的。

ARM处理器结 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)