PCB布线原则

本章及随后几章将讨论静电放电引起的系统问题的硬件解决措施。为了便于对系统硬件解决进行讨论,将系统上的静电放电效应划分成以下三个部分:

1. 静电放电之前静电场的效应

2. 放电产生的电荷注入效应

3. 静电放电电流产生的场效应

尽管印刷线路板(PWB,通常也称之为PCB)的设计会对上述三种效应都产生影响,但是主要是对第三种效应产生影响。下面的讨论将针对第三条所述的问题给出设计指南。通常,源与接收电路之间的场耦合可以通过下列方式之一减小(这些通用方法也会在其它讨论场的章节中提到):

1. 在源端使用滤波器以衰减信号

2. 在接收端使用滤波器以衰减信号

3. 增加距离以减小耦合

4. 降低源和/或接收电路的天线效果以减小耦合

5. 将接收天线与发射天线垂直放置以减小耦合

6. 在接收天线与发射天线之间加屏蔽

7. 减小发射及接收天线的阻抗来减小电场耦合

8. 增加发射或接收天线之一的阻抗来减小磁场耦合

9. 采用一致的、低阻抗参考平面(如同多层PCB 板所提供的)耦合信号,使它们保持共模方式

在具体设计中,如电场或磁场占主导地位,应用方法7 和8 就可以解决。然而,静电放电一般同时产生电场和磁场,这说明方法7 将改善电场的抗扰度,但同时会使磁场的抗扰度降低。方法8 则与方法7 带来的效果相反。所以,方法7 和8并不是完善的解决方案。不管是电场还是磁场,使用方法1 ~ 6 与9 都会取得一定的效果,但PCB 设计的解决方法主要取决于方法3 ~ 6 和9 的综合使用。

下面详细阐述通过方法 3 ~ 6 和9 解决问题的六条实践法则及其原因所在。

一、保持环路面积最小

任意一个电路回路中有变化的磁通量穿过时,将会在环路内感应出电流。电流的大小与磁通量成正比。较小的环路中通过的磁通量也较少,因此感应出的电流也较小,这就说明环路面积必须最小。应用这一经验的困难之处是如何找到环路。

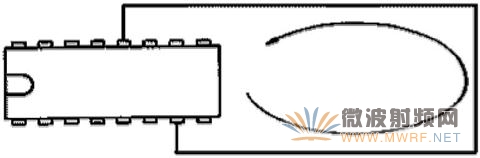

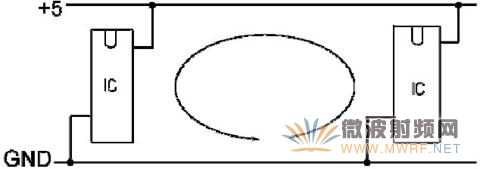

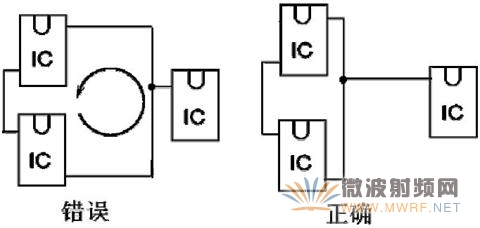

每个人都知道图16 中所示的环路,但要正确识别图17 中所示的环路则比较困难。

图 16 简单的PCB 回路

图 17 电源线与地线构成的PCB 回路

与其试着去找出所有可能的环路,还不如采取下列步骤来减小环路面积:

A、电源线与地线应紧靠在一起以减小电源和地间的环路面积。

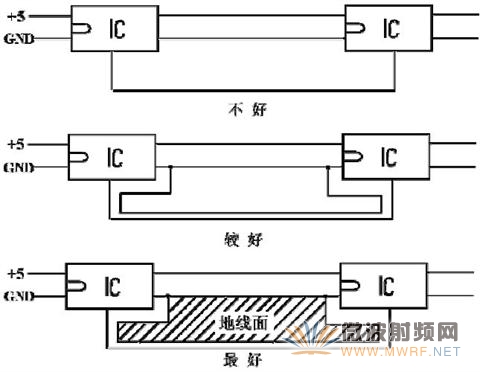

图 18 示例说明了电源线与地线同集成电路连接的几种不同方法。

图 18 电源与地形成的环路面积的减小

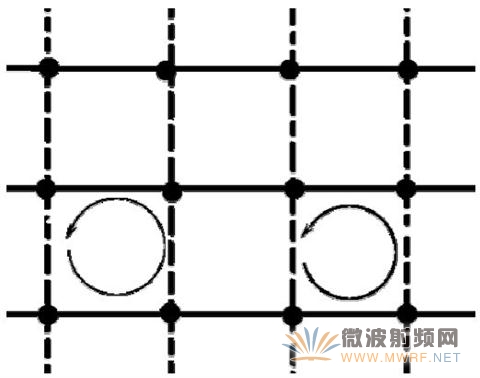

B、多条电源及地线应连接成网格状。

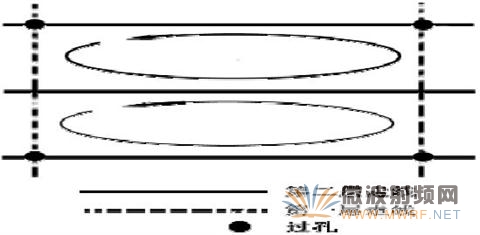

图19 和图20 说明了这一点:在这个典型的PCB 设计中,PCB 的一面布垂直线,而另一面则布水平线(此图中仅画出地线)。如图19 所示,这个典型的地线结构会使环路面积很大,可以在双面板上添加一些连接线以减小环路面积,如图20 所示。网格构成的环路面积小得多,这将使感应电流很低,出现问题的可能性也较小。插在底板(或母板)PCB 上的PCB 板,应该有多个地线和电源线节点,且在连接器长度方向上均匀布置。这将有利于减小整个系统的环路面积。

图 19 典型的PCB 地线结构

图 20 地线网格

上述步骤 A 和B 既可减小电源与地之间的环路面积,同时也可减小环路天线的效能,下面讲的步骤C 和D 将降低天 线及信号线的效率。 C、并联的导线必须紧紧地放在一起,最好仅使用一条粗导线。图 21 表明了这一原则。这就是说,地平面不应有大 的开口,因为这些开口如同平行导线一般,其作用等同于环路天线。

图 21 缩短平行路径

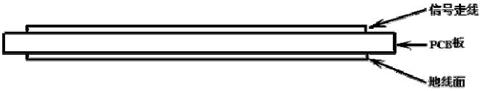

D、信号线应与地线应紧挨着放在一起。在每根信号线的旁边安排一条地线。不过,这也许会产生很多平行地线。为 了避免这个问题,如前所述,可采用地平面或地线网格,而不采用单条地线。一个例子如图22 所示。在这里,假设由于某种原因信号线不能移动。

图 22 信号线与地线紧挨着布线

可在与信号线相对的一面上布置地线面,如图 23 所示。实际上,将空余PCB 部分填以地线面是个好办法。

图 23 信号线与地线或地平面的分层布线

E、特别敏感的器件之间的较长的电源线或信号线应每隔一定间隔与地线的位置对调一下。对调的含义是将一根 导线从上移到下面,或从左边移到右边,另一根导线则做相反的调整。图24 表明了这种方法与减小环路面积的等同效果: 对调有关导线后,只有较小的环路存在。

F、在电源线与地线间安装高频旁路电容。因为在静电放电较低的频率段,旁路电容的阻抗较低,在这些频率处, 旁路电容能有效减小电源与地间的环路面积。然而,在静电放电较高的频率段,由于寄生电感的影响,即使是高频电容, 其作用也很有限。当然,电源线与地线彼此靠得越近,滤波电容的效果就越不明显。因为环路面积已经足够小了。图 25 和26 说明了这种效果。即使在每个元件旁边都安装

PCB布线 相关文章:

- 从实践角度探讨高速PCB的布线问题(07-03)

- PCB布线规则详解(12-02)

- 优化PCB布线减少串扰的解决方案(08-09)