PCB布线原则

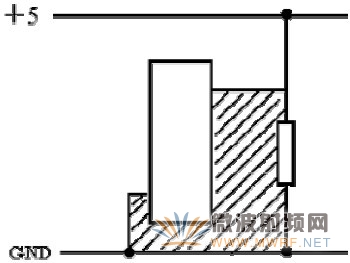

旁路电容器,图25 中的电路仍有很大的环路面积。

图 25 安装旁路电容器的大环路面积

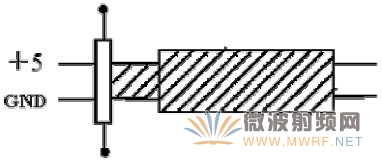

图 26 安装旁路电容的小环路面积

图 26 中所示的电路,由于将电源线与地线紧挨着放在一起布置,使得环路面积大大减小。然而,即使将电源线与地线 并列分布,较长的导线仍会导致较大的环路面积。

二、使导线长度尽量短

天线要具有较高的效率,其长度必须是波长 很大的一部分。这就是说,较长的导线将有利于接收静电放电脉冲产生的更多的频率成份;而较短的导线只能接收较少的频 率成分。因此,短导线从静电放电产生的电磁场中接收并馈入电路的能量较少。使导线尽可能短是一个比是环路面积尽 量小更容易实现的措施。因为它不象信号环路那样不容易识别,环路面积的尽可能小不可能立即看到,而导线的长短则是很显然的。有关设计步骤如下:

a) 使所有元件紧靠在一起,PCB 设计人员不应将元件过于分散而占用更多的面积;

b) 在相关的元件组,相互之间具有很多互连线的元件应彼此靠得很近。例如,I/O 器件是与I/O 连接器尽量靠得近些;

c) 如有可能的话,从线路板的中心馈送电源或信号,而不要从线路板边缘馈送,如图27 所示,中间的馈送信号使大多数元件的 连线最短。当线路板为正方形时,这样做的效果最明显,当线路板狭长时,效果则不很明显。

但只要可能,还是应该尽量这样做。前面提出的 PCB 设计规则主要针对静电放电电流产生的场效应。但值得注意的是,前面介绍的降低天线效率的方法,这也有助于防止共模噪声转化成会带来更大麻烦的差模噪声,这在本章开始列出的一般性方法的第9 条中已提及过。

之所以有这样的效果,是因为前述的各种步骤都有助于减小各种PCB 回路的阻抗差异。例如,规则一中的步骤D 特别有用, 因为这样处理会使信号线与相关地线的回路阻抗几乎相等。因此,串入到这两条路径中的共模噪声在幅度上也很接近,产生 的差模噪声极小。另外,PCB 设计也能采取措施减小由于静电场和电荷注入所带来的问题。下面讲述的规则就与这个问题 有关,你会发现有几个规则与前述规则相同。

三、尽可能在 PCB 上使用完整的地线面(建议采用多层板)

前面已提到过,地线面有助于减小环路面积,同时也降低了接收天线的效率。地线面作为一个重要的电荷源,可抵消静电放电源上的 电荷,这有利于减小静电场带来的问题。PCB 地线面也可作为其对面信号线的屏蔽体(当然,地线面的开口越大,其屏蔽效能就越低)。另外,如果发生放电,由于PCB 板的地平面很大,电荷很容易注入到地线面中,而不是进入到信号线中。 这样将有利于对元件进行保护,因为在引起元件损坏前,电荷可以泄放掉。(然而,即使泄放到地的电荷也可能损坏器件,应采取措施加以避免)

四、加强电源线和地线之间的电容耦合

电源线与地线间的耦合通过两种方式来实现,这在前面已经提到过。

A、使电源线与地线靠得很近,或采用多层PCB 板。这将在电源线和地线间产生更多的寄生电容。

B、 在电源线与地线之间接入高频旁路电容(电容组合方式可适用于静电放电频率较低和较高的场合)。电源线与地线间的耦合 将有助于减小电荷注入问题。两个物体之间由各个物体上电荷量的差异造成的电压取决于两者(V=Q/C)间的电容。如果X 库仑的电荷注入到电源线中,就会在电源线和地线间产生Y 伏的电压。如果电源线与地线间的电容增加一倍,X 库仑的电 荷将仅仅产生Y/2 伏的电压。当然,这个较小的电压造成损坏的可能性也相应减小。

五、隔离电子元件与静电放电电荷源

在静电放电效应的讨论中,曾指出注入到电子仪器中的电荷可通过隔离来解决。对于 PCB 设计,这主要指将电子仪器与可能的电荷源隔离开,也与连接器端口或感应电流趋于集中的信号线相隔离。可采取以下两个步骤来进行隔离:

A、使电子元件与PCB 走线远离会暴露在静电放电中的PCB 部分(例如,操作人员可直接触摸到的地方)。

B、使电子元件 和PCB 走线远离会暴露在静电放电中的任意一个金属物体(包括螺钉、机架、连接器外壳等)。后一个要求小于下面的设 计规则相关联。

六、PCB 上的机壳地线的阻抗要低,隔离要好

尽管 PCB 轨线上的阻焊层有利于隔离PCB 走线,但阻 焊层可能会导致插针孔发生电弧。

A、隔离机壳地线的最好方法是使之远离电子仪器。另外,如果机壳地线的阻抗很低,静电放电电流易于通过,就不会发生电弧。当然,如此迅速的电荷泄放会产生更强的场,但这比电荷通过电弧直接注入 到电路中好得多。

B、机壳地线的长度不能超过其宽度的四或五倍。比这个比例更宽的地线仅能使其阻抗(电感)稍微减小,但是更窄的地线却会使其阻抗大幅度增加。这个长宽比例意味着机壳地线必须很短才行,否则当地线增长时,其宽度要很宽。

PCB布线 相关文章:

- 从实践角度探讨高速PCB的布线问题(07-03)

- PCB布线规则详解(12-02)

- 优化PCB布线减少串扰的解决方案(08-09)