S3C2410中断机制及相关寄存器介绍

t to 1. This does not cause the bit of INTPND register changed. When a pending bit of the INTPND register is set, the interrupt service routine starts whenever the I-flag or F-flag is cleared to 0. The SRCPND and INTPND registers can be read and written, so the service routine must clear the pending condition by writing a 1 to the corresponding bit in the SRCPND register first and then clear the pending condition in the INTPND registers by using the same method.

Interrupt Mask Register

This register indicates that an interrupt has been disabled if the corresponding mask bit is set to 1. If an interrupt mask bit of INTMSK is 0, the interrupt will be serviced normally. If the corresponding mask bit is 1 and the interrupt is generated, the source pending bit will be set.

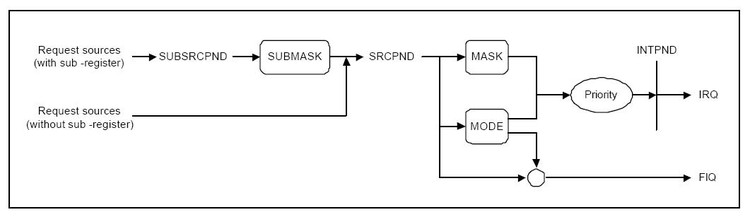

S3C2410的中断控制器原理如图1-2所示。

图1-2中断控制器原理

由上图可以看出S3C2410的中断控制器主要通过几个控制寄存器来实现:中断源待决寄存器(Source Pending Register,SRCPND/SUBSRCPND)、中断模式寄存器(Interrupt Mode Register,INTMOD)、中断屏蔽寄存器(Interrupt Mask Register,INTMASK/INTSUBMSK)、中断优先级控制寄存器(IRQ PRIORITY Control Register,PRIORITY)、中断待决寄存器(Interrupt Pending Register,INTPND)。

该图也显示了S3C2410的中断处理流程:首先要有中断源产生中断,这里面有两条路径表示中断源,上面一条是次级中断源,当次级中断产生后,首先在SUBSRCPND寄存器中登记,然后经过次级屏蔽寄存器(SUBMASK)来决定这个次级中断源所产生的中断是否被屏蔽掉,被屏蔽掉的中断将不会被执行。次级中断源所产生的中断在经过SUBMASK之后将会与主中断源所产生的中断汇合,然后在SRCPND寄存器中登记,再经过主屏蔽寄存器,得出该中断是否被送往CPU处理的决定。当然,在送往CPU处理之前,还要根据中断模式寄存器的设置判断一下该中断是属于IRQ中断还是FIQ中断,如果是FIQ中断则直接触发。如果是IRQ中断,则还要判断中断的优先级别,级别高的先执行。

(1)中断源待决寄存器SRCPND/ SUBSRCPND

这两个寄存器在功能上是相同的,它们是中断源待决寄存器。在一个中断处理流程中,中断信号传进中断控制器后首先遇到的就是SRCPND/ SUBSRCPND,这两个寄存器的作用是用于标示出哪个中断请求被触发。SRCPND的有效位为32,SUBSRCPND的有效位为11,它们中的每一位分别代表一个中断源。SRCPND为主中断源待决寄存器,SUBSRCPND为次中断源待决寄存器。

The SRCPND register is composed of 32 bits each of which is related to an interrupt source. Each bit is set to 1 if the corresponding interrupt source generates the interrupt request and waits for the interrupt to be serviced. Accordingly, this register indicates which interrupt source is waiting for the request to be serviced. Note that each bit of the SRCPND register is automatically set by the interrupt sources regardless of the masking bits in the INTMASK register. In addition, the SRCPND register is not affected by the priority logic of interrupt controller.

In the interrupt service routine for a specific interrupt source, the corresponding bit of the SRCPND register has to be cleared to get the interrupt request from the same source correctly. If you return from the ISR without clearing the bit, the interrupt controller operates as if another interrupt request came in from the same source. In other words, if a specific bit of the SRCPND register is set to 1, it is always considered as a valid interrupt request waiting to be serviced.

The time to clear the corresponding bit depends on the users requirement. If you want to receive another valid request from the same source, you should clear the corresponding bit first, and then enable the interrupt.

You can clear a specific bit of the SRCPND register by writing a data to this register.It clears only the bit positions of the SRCPND corresponding to those set to one

S3C2410中断机制寄存 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)