ARM系列之时钟模块详述及其分频系数的设定

要48MHz的频率,所以源频率,即UPLL只能为48或者96。

--------------------------------ooo------------------------------------------

讲到这里,重点都说了哇,不多还有些特别的东西需要提出来下。

1. 在arm的体系中,还存在一个概念,叫做慢时钟模式的概念,即将时钟减半或者关闭,以减少能源消耗。可以通过CLKSLOW和CLKdivN寄存器相互配合实现。如下图所示:

2. arm体系中很多模块都需要时钟,要是能够将不需要使用时钟的外设的时钟共用给关了,也能减少消耗,在arm中提供了这样的寄存器给予定制,即CLKCON寄存器。

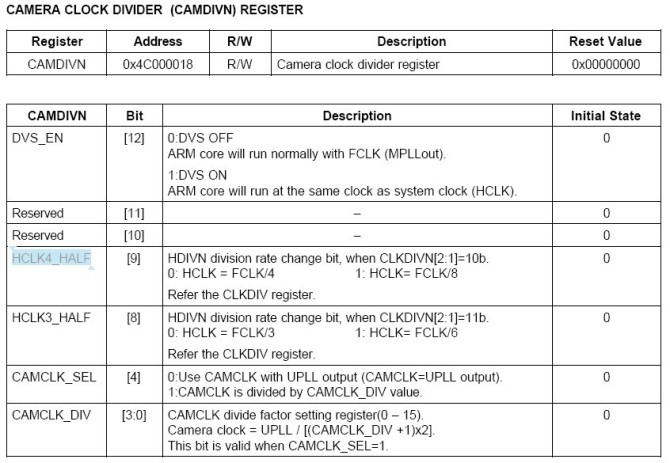

3. 专门用于相机时钟设定的寄存器CAMdivN。如下图所示,在分频时候用到了HCLK4_HALF、HCLK3_HALF。

没了~~~

------------over----------------------------------------

样例程序如下:

[PLL_ON_START; //设置CLKdivN的值在PLL锁存时间LOCKTIME之后有效。

;Configure FCLK:HCLK:PCLK

ldrr0,=CLKdivN

ldrr1,=CLKdiv_VAL;CLKdiv_VAL=7,7=1:3:6. Fclk:Hclk:Pclk

strr1,[r0]

;Configure UPLL //UPLL

ldrr0,=UPLLCON

ldrr1,=((U_Mdiv<12)+(U_Pdiv<4)+U_Sdiv) ; //Fin = 12.0MHz, UCLK = 48MHz

strr1,[r0]

;Configure MPLL //MPLL

ldrr0,=MPLLCON

ldrr1,=((M_Mdiv<12)+(M_Pdiv<4)+M_Sdiv) ; //Fin = 12.0MHz, FCLK = 400MHz

strr1,[r0]

]

END.!!!

ARM系列时钟模块分频系 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)