ARM系列之时钟模块详述及其分频系数的设定

-------------------------------------o---------------------------------------------------------

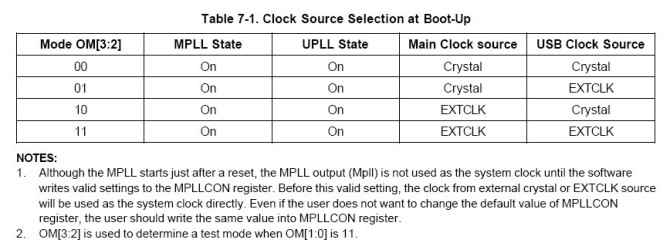

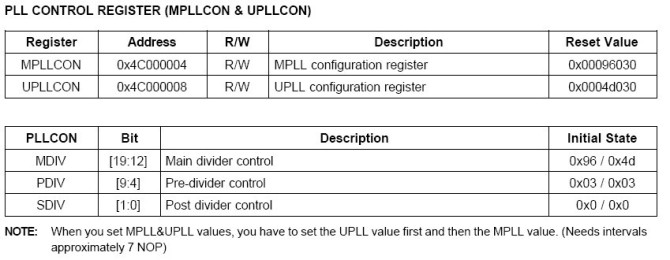

关于时钟源选择的问题,主要时钟源一个来自于外部晶振(XTlpll),一个来自于外部时钟(EXTCLK)。时钟发生器包括一个连接到外部晶振的振荡器和两个锁相环(PLL)。 时钟源的选择可以通过芯片引脚的状态进行配置,即芯片的OM3和OM2引脚。具体分配情况如下表所示:(原理图中已经将OM3和OM2都接地,即00的情况,用的是外部晶振,而且晶振频率为12MHz)。.

---------------------------o-----------------------------------------------------

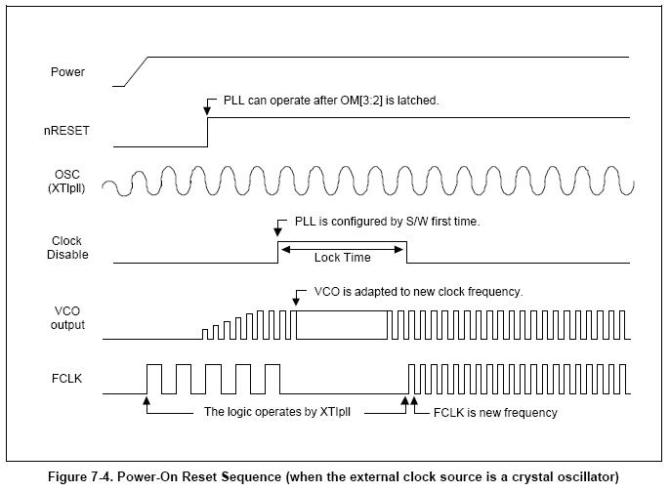

具体分频寄存器设置时序如下图所示:(尽管MPLL在系统复位的时候就开始产生,但是只有有效的设置好MPLLCON寄存器后才能用于系统时钟。在此之前,外部时钟将直接作为系统时钟。即使不需要改变MPLLCON寄存器的初值,也必须将同样的值写入寄存器。设置完成后,经过LOCKTIME的时间,设置的分频才能起效果。)

如上图所示,FCLK的启动过程:

1、上电几毫秒后,晶振输出稳定,FCLK=晶振频率,nRESET信号恢复高电平后,CPU开始执行指令。

2、我们可以在程序开头启动MPLL,在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。

3、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。LOCKTIME默认时间为200us。

-----------------------------------------o-------------------------------------------------

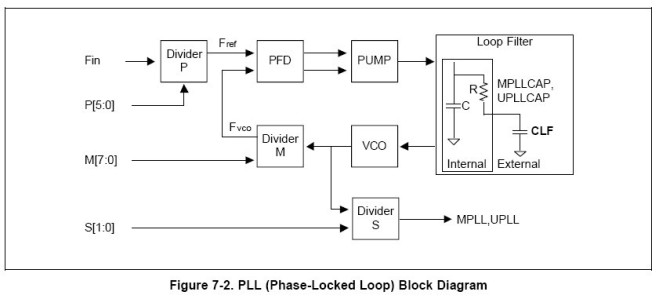

时钟分频流程如下图所示:(Fin默认为外部晶振时钟频率,12MHz。)

位于时钟信号发生器的内部MPLL用于将输出信号和相关输入信号在相位和频率上同步起来。包括上图所示的一些基本模块:根据DC电压产生相应比例关系频率的压控振荡器VCO,出书P(对输入频率Fin进行分频),除数M(对VCO的输出频率进行M分频,分频后输入到相位频率探测器PFD),除数S(对MPLL输出频率Mpll进行分频),相差探测器,charge pump,loop filter。

----------------------------o------------------------------------------------

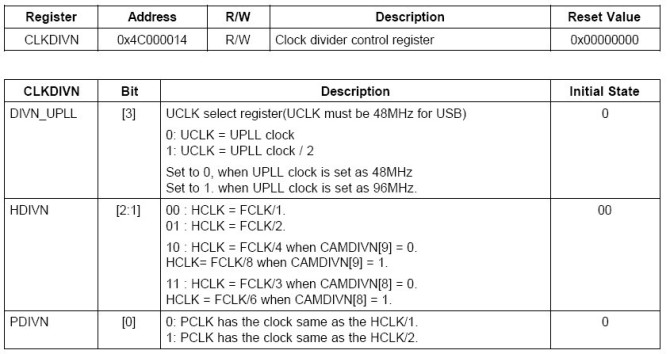

时钟频率的计算关系:FCLK,HCLK,PCLK.(其中已经知道用于USB的UCLK位48MHz。)

一般情况下,这三个始终之间是存在一定的额比例关系的,默认情况下为1:1:1。但是通常情况下会设置为1:4:8或者1:3:6。寄存器CLKdivN用于设置这三者之间的比例关系。

也就是说,如果CLKdivN设置为0x5,那么比例即为1:4:8,前提是CAMdivN[9]为0.也就说如果主频FLCK是400MHz,按照1:4:8的设置,那么HLCK是100MHz,PLCK是50MHz。讲到这里主题也该突出,说到最后,问题的关键就是如何计算FCLK了吧!!!

--------------------------------ooo------------------------------------------

现在的CPU主频都是通过倍频的技术实现的,下面就描述下如何个倍频法:

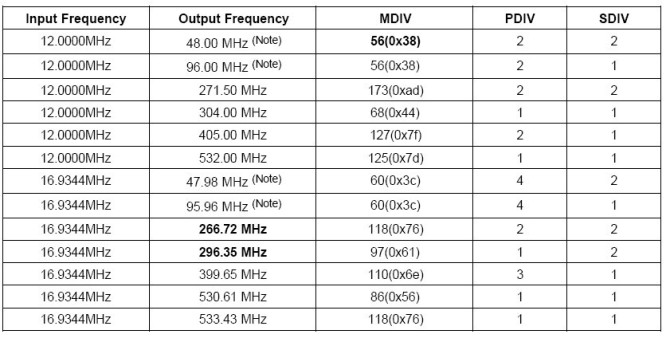

1. MPLL. 对于S3C2440来说,常用的输入Fin主要有两种频率:12MHz和16.935MHz。CPU通过Mdiv、Pdiv和Sdiv进行倍频得到MPLL,即FCLK。公式如下所示:

Mpll = (2 * m * Fin) / (p * 2^S)

m = (Mdiv + 8), p = (Pdiv + 2), s = Sdiv; 1<=M<=248,1<=P<=62

理论上,我们可以通过设置任意值而得到我们想要的频率,然而由于实际存在种种的约束关系,设置一个适当的频率不容易,手册中推荐了如下的设置值:

例如,假设输入时钟FIN=16.9344M,Mdiv=110, Pdiv=3, Sdiv=1,利用上面的公式,FCLK=2*16.9344*(110+8)/((2+3)*2)=399.65 MHz。

2. UPLL.上面已经详细的描述了MPLL的设置过程。下面着重描述USB的使用频率UPLL的设置。需要对UPLLCON寄存器设置,如上上图所示。同样也可以通过查表。

Upll = (m * Fin) / (p * 2^S)

m = (Mdiv + 8), p = (Pdiv + 2), s = Sdiv

需要注意的是CLKdivN寄存器的第三位divN_UPLL用来设置USB时钟UCLK和UPLL的关系,如果UPLL已经是48Mhz了,那么这一位应该设置为0,表示1:1的关系,否则是1:2的关系。由于目标USB只需

ARM系列时钟模块分频系 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)