前段时间用

STM32F103VBT6写了一个中断的函数,借此机会想了解下STM32的中断机制,用过之后发现STM32的中断配置相当灵活,稳定行很高,测试发现几乎没出过什么差错。我在程序里开了三个中断,一个计数器用于精确延时用,另外两个为外部事件处理中断,下面一一详细介绍,方便初学者入门。

在进行STM32中断配置之前首先需要了解下它的中断部分:

一、Cortex-M3中断机制

在STM32处理器中有43个可屏蔽中断通道(?包含 16个 Cortex?-M3的中断线)。共设置了16个可编程的优先等级(使用? 4位中断优先级);它的嵌套向?中断控制器(NVIC)和处?器核的接口紧密相连,可以实现低延迟的中断处?和有效处?地处?晚到的中断。嵌套向?中断控制器管?着包括核异常等中断。

Cortex—M3是一个32位的核,在传统的单片机领域中,有一些不同于通用32位CPU应用的要求。比如在工控领域,用户要求具有更快的中断速度,Cortex-M3采用了Tail-Chaining中断技术,完全基于硬件进行中断处理,最多可减少12个时钟周期数,在实际应用中可减少70%中断。

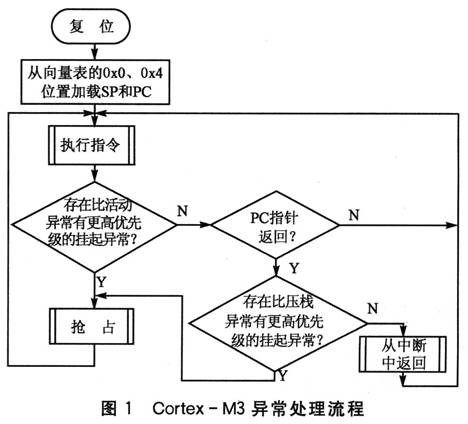

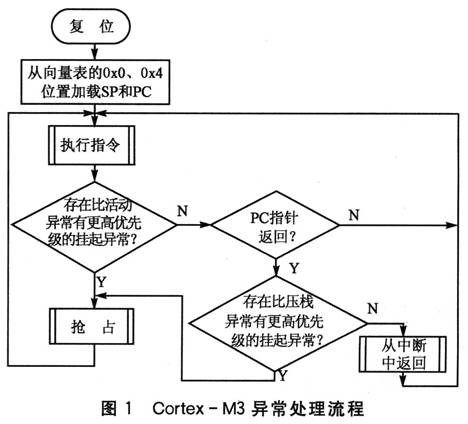

异常或者中断是处理器响应系统中突发事件的一种机制。当异常发生时,Cortex—M3通过硬件自动将编程计数器(PC)、编程状态寄存器(XPSR)、链接寄存器(LR)和R0~R3、R12等寄存器压进堆栈。在Dbus(数据总线)保存处理器状态的同时,处理器通过Ibus(指令总线)从一个可以重新定位的向量表中识别出异常向量,并获取ISR函数的地址,也就是保护现场与取异常向量是并行处理的。一旦压栈和取指令完成,中断服务程序或故障处理程序就开始执行。执行完ISR,硬件进行出栈操作,中断前的程序恢复正常执行。图1为Cortex—M3处理器的异常处理流程。

二、STM32 SysTick 介绍

Cortex-M3的内核中包含一个SysTick时钟。SysTick为一个24位递减计数器,SysTick设定初值并使能后,每经过1个系统时钟周期,计数值就减1 。计数到0时SysTick计数器自动重装初值并继续计数,同时内部的COUNTFLAG 标志会置位,触发中断( 如果中断使能情况下 ) 。

对于STM32系列微处理器来说,执行一条指令只有几十个 ns ,进行 for 循环时,要实现N毫秒的x值非大,而且由于系统频率的宽广,很难计算出延时N毫秒的精确值。针对STM32微处理器,需要重新设计一个新的方法去实现该功能,因此,在STM32的应用中,使用Cortex-M3内核的SysTick 作为定时时钟,设定每一毫秒产生一次中断,在中断处理函数里对N减一,在Delay(N)函数中循环检测N是否为0,不为0则进行循环等待;若为 0 则关闭 SysTick 时钟,退出函数,这种延时函数的做法能很高效地实现精确定时。

三、SysTick编程实现Delay(N)函数

思路:利用systick定时器为递减计数器,设定初值并使能它后,它会每个系统时钟周期计数器减 1 ,计数到 0 时 ,SysTick 计数器自动重装初值并继续计数,同时触发中断 。那么每次计数器减到 0 ,

时间经过了:

T = 系统时钟周期x计数器初值

比如使用 72M 作为系统时钟,那么每次计数器减 1 所用的时间是 1/72M ,计数器的初值如果是 72000 , 那么每次计数器减到 0 , 时间经过 (1/72M) * 72000 =0.001s ,即 1ms.

有了以上思路做铺垫后,为了实现首先我们需要一个72MHz的SysTick时钟。

第一步 配置RCC寄存器和SysTick寄存器

由于系统时钟(SysTick)可选择为PLL输出、HSI或者HSE,在这里选择9倍频的PLL作为SysTick的时钟源,同时HCLK(AHB Clock)时钟也相应的配置成72MHz了,因为最终SysTick是需要通过AHB后输出的,所以在配置的同时也需要选择AHB 时钟,这里选择为RCC_SYSCLK_Div1(咖啡色部分)表示AHB 时钟 = 系统时钟,相关配置见下面函数(RCC_Configuration)红色字体部分。这里需要特别强调一点,有关书籍里常提到"SysTick的最高频率为 9MHz (最大为HCLK/ 8),在这个条件下,把SysTick重装载值设置为9000,将SysTick时钟设置为9MHz,就能够产生1ms 的时间基值"刚开始对这句话感到很迷惑,因为,有的地方介绍SysTick没有说最大频率智能9MHz,这里却指出会被8分频,两者出现了矛盾!相信有过我这种疑惑的人不在少数!究其原因我猜想是原文作者没有说明这点,转载的人见到有相关的知识便直接转载了,自己也没去想,估计也没弄明白过,这样便一个个都转开了,所以我建议在吸取别人精华时要多多思考,只有注入了自己的新元素知识才是被真正吸收了,否则即使涉猎的再多,也只是收藏!现在再来分析下上面的那个矛盾点,其实应该这么理解的,在STM32中,SysTick的架构其实是这么回事的:首先选择时钟源-->AHB-->这里便分走两路,其一被8分频,也便出现了最高频率9MHz的结果;其二作为FCLK(CM3上的自由运行时钟)直接从AHB输出,这里却是没有再分频的,其频率就是AHB时钟频率,最大可以达到72MHz,下面程序对其设置也是在72MHz的的情况下的,具体可以参考STM32时钟架构这幅图,如下: