S3C2440 SDRAM内存驱动

时间:11-20

来源:互联网

点击:

休眠模式低功耗状态下的数据保存,这方面最著名的应用就是STR(Suspend to RAM,休眠挂起于内存)。在发出AR命令时,将CKE置于无效状态,就进入了SR模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

SDRAM相关寄存器:

(1)BWSCON寄存器(BUS WIDTH & WAIT CONTROL REGISTER)

表2-17 SDRAM控制寄存器(BWSCON)

根据开发板的存储器配置和芯片型号,设置每个BANK焊接芯片的位宽和等待状态

BWSCON,每4位对应一个BANK,这4位分别表示:

lSTx:启动/禁止SDRAM的数据掩码引脚(UB/LB),SDRAM没有高低位掩码引脚,此位为0,SRAM连接有UB/LB管脚,设置为1

l注:UB/LB数据掩码引脚用来控制芯片读取/写入的高字节和低字节(对比硬件手册SDRAM和SRAM的接线图)

lWSx:是否使用存储器的WAIT信号,通常设为0

lDWx:设置焊接存储器芯片的位宽,笔者开发板使用两片容量为32M,位宽为16的SDRAM组成64M,32位存储器,因此DW7,DW6位设置为0b10,其它BANK不用设置采用默认值即可。

lBANK0对应的是系统引导BANK,这4位比较特殊,它的设置是由硬件跳线决定的,因此不用设置

lBWSCON设置结果:0x22000000

(2)BANKCON0~BANKCON5 (BANK CONTROL REGISTER)

表2-18 BANKCON0~BANKCON5控制寄存器(BANKCON0~BANKCON5)

这6个寄存器用来设置对应BANK0~BANK5的访问时序,采用默认值0x700即可

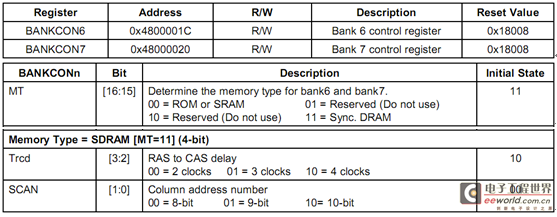

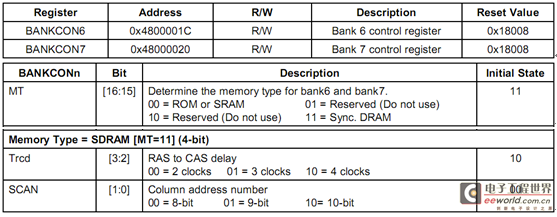

(3)BANKCON6~BANKCON7 (BANK CONTROL REGISTER)

表2-19 BANKCON6~BANKCON7控制寄存器(BANKCON6~BANKCON7)

由于内存都焊接在这两个BANK上,因此内存驱动主要是对这两个寄存器进行设置

lMT:设置BANK6~BANK7的存储器类型,

00=ROM or SRAM 01=保留

10=保留11=SDRAM

内存为SDRAM,设置为0b11,对应的应该设置Trcd和SCAN位,其它位和SDRAM无关

lTrcd:RAS to CAS Delay行地址选通到列地址选通延迟,这个参数请看后面的内存工作原理扩展部分解释,笔者内存芯片为HY57V561620,由其芯片手册可知其Trcd为最少20ns,如果内存工作在100MHz,则该值至少要为2个时钟周期,通常设置为3个时钟周期,因此设置为0b01

lSCAN:SDRAM Column Address Number SDRAM的列地址数,笔者内存芯片为HY57V561620,列地址数为9,设置为0b01

lBANK6,BANK7设置结果为:0x18005

(4)REFRESH (REFRESH CONTROL REGISTER)

表2-20刷新频率设置寄存器(REFRESH)

SDRAM的刷新有效,刷新频率设置寄存器(刷新)

lREFEN:开启/关闭刷新功能,设置为1,开启刷新

lTREFMD:SDRAM刷新模式,0=CBR/AutoRefresh,1=Self Refresh,设置为0,自动刷新

lTrp:行地址选通预充电时间,一般设置为0b00即可

lTsrc:单行刷新时间,设置为0b11即可。

lRefresh Counter:内存存储单元刷新数,它通过下面公式计算出:

Refresh Counter = 2^11 + 1 – SDRAM时钟频率(MHz)* SDRAM刷新周期(uS)

SDRAM的刷新周期,也就是内存存储单元间隔需要多久进行一次刷新,前面内存工作原理分析可知电容数据保存上限为64ms,笔者使用内存芯片每个L-Bank共有8192行,因此每次刷新最大间隔为:64ms/8192 = 7.8125uS,如果内存工作在外部晶振频率12MHz下,Refresh Counter = 1955,如果内存工作在100MHz下,那么Refresh Counter = 1269(取大整数)

lREFRESH寄存器设置为:

0x8e0000 + 1269 = 0x008e04f5(HCLK = 100MHz)

0x8e0000 + 1955 = 0x008e07a3(HCLK = 12MHz)

(5)BANKSIZE寄存器(BANKSIZE REGISTER)

表2-21 BANKSIZE寄存器(BANKSIZE)

设置内存的突发传输模式,省电模式和内存容量。

lBURST_EN:是否开启突发模式,0 = ARM内核禁止突发传输1 =开启突发传输,设置为1,开启突发传输

lSCKE_EN:是否使用SCKE信号作为省电模式控制信号,0 =不使用SCKE信号作为省电模式控制信号1 =使用SCKE信号作为省电模式控制信号,通常设置为1

lSCLK_EN: 设置向存储器输入工作频率,0 =一直输入SCLK频率,即使没有内存操作也会输入,1 =仅当进行内存数据操作时才输入SCLK频率,通常设置为1

lBK76MAP:设置Bank6/7的内存容量,笔者使用开发板内存为两片32M内存芯片并联成64M,它们全部都外接到Bank6上,因此选择0b001

lBANKSIZE寄存器设置为:0xb1

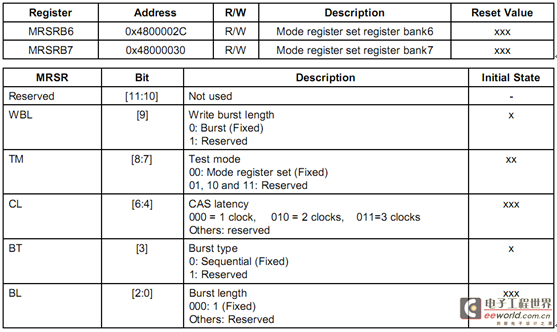

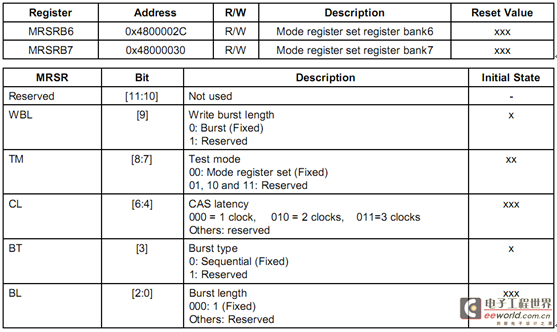

(6)SDRAM模式设置寄存器MRSRx (SDRAM MODE REGISTER SET REGISTER)

表2-22 SDRAM模式设置寄存器(MRSRx)

该寄存器用于设置CAS潜伏周期,可以手动设置的位只有CL[6:4]位,通过前面内存工作原理可知,笔者使用开发板CL=3,即0b011

lMRSR6,MRSR7设置为:0x00000030

图2-55设置加载时运行时地址

init.s:本程序文件主要实现了,关闭看门狗,初始化内存,拷贝ROM数据到内存中,然后跳往内存中执行xmain函数,从xmain函数返回之后,将全部

SDRAM相关寄存器:

(1)BWSCON寄存器(BUS WIDTH & WAIT CONTROL REGISTER)

表2-17 SDRAM控制寄存器(BWSCON)

根据开发板的存储器配置和芯片型号,设置每个BANK焊接芯片的位宽和等待状态

BWSCON,每4位对应一个BANK,这4位分别表示:

lSTx:启动/禁止SDRAM的数据掩码引脚(UB/LB),SDRAM没有高低位掩码引脚,此位为0,SRAM连接有UB/LB管脚,设置为1

l注:UB/LB数据掩码引脚用来控制芯片读取/写入的高字节和低字节(对比硬件手册SDRAM和SRAM的接线图)

lWSx:是否使用存储器的WAIT信号,通常设为0

lDWx:设置焊接存储器芯片的位宽,笔者开发板使用两片容量为32M,位宽为16的SDRAM组成64M,32位存储器,因此DW7,DW6位设置为0b10,其它BANK不用设置采用默认值即可。

lBANK0对应的是系统引导BANK,这4位比较特殊,它的设置是由硬件跳线决定的,因此不用设置

lBWSCON设置结果:0x22000000

(2)BANKCON0~BANKCON5 (BANK CONTROL REGISTER)

表2-18 BANKCON0~BANKCON5控制寄存器(BANKCON0~BANKCON5)

这6个寄存器用来设置对应BANK0~BANK5的访问时序,采用默认值0x700即可

(3)BANKCON6~BANKCON7 (BANK CONTROL REGISTER)

表2-19 BANKCON6~BANKCON7控制寄存器(BANKCON6~BANKCON7)

由于内存都焊接在这两个BANK上,因此内存驱动主要是对这两个寄存器进行设置

lMT:设置BANK6~BANK7的存储器类型,

00=ROM or SRAM 01=保留

10=保留11=SDRAM

内存为SDRAM,设置为0b11,对应的应该设置Trcd和SCAN位,其它位和SDRAM无关

lTrcd:RAS to CAS Delay行地址选通到列地址选通延迟,这个参数请看后面的内存工作原理扩展部分解释,笔者内存芯片为HY57V561620,由其芯片手册可知其Trcd为最少20ns,如果内存工作在100MHz,则该值至少要为2个时钟周期,通常设置为3个时钟周期,因此设置为0b01

lSCAN:SDRAM Column Address Number SDRAM的列地址数,笔者内存芯片为HY57V561620,列地址数为9,设置为0b01

lBANK6,BANK7设置结果为:0x18005

(4)REFRESH (REFRESH CONTROL REGISTER)

表2-20刷新频率设置寄存器(REFRESH)

SDRAM的刷新有效,刷新频率设置寄存器(刷新)

lREFEN:开启/关闭刷新功能,设置为1,开启刷新

lTREFMD:SDRAM刷新模式,0=CBR/AutoRefresh,1=Self Refresh,设置为0,自动刷新

lTrp:行地址选通预充电时间,一般设置为0b00即可

lTsrc:单行刷新时间,设置为0b11即可。

lRefresh Counter:内存存储单元刷新数,它通过下面公式计算出:

Refresh Counter = 2^11 + 1 – SDRAM时钟频率(MHz)* SDRAM刷新周期(uS)

SDRAM的刷新周期,也就是内存存储单元间隔需要多久进行一次刷新,前面内存工作原理分析可知电容数据保存上限为64ms,笔者使用内存芯片每个L-Bank共有8192行,因此每次刷新最大间隔为:64ms/8192 = 7.8125uS,如果内存工作在外部晶振频率12MHz下,Refresh Counter = 1955,如果内存工作在100MHz下,那么Refresh Counter = 1269(取大整数)

lREFRESH寄存器设置为:

0x8e0000 + 1269 = 0x008e04f5(HCLK = 100MHz)

0x8e0000 + 1955 = 0x008e07a3(HCLK = 12MHz)

(5)BANKSIZE寄存器(BANKSIZE REGISTER)

表2-21 BANKSIZE寄存器(BANKSIZE)

设置内存的突发传输模式,省电模式和内存容量。

lBURST_EN:是否开启突发模式,0 = ARM内核禁止突发传输1 =开启突发传输,设置为1,开启突发传输

lSCKE_EN:是否使用SCKE信号作为省电模式控制信号,0 =不使用SCKE信号作为省电模式控制信号1 =使用SCKE信号作为省电模式控制信号,通常设置为1

lSCLK_EN: 设置向存储器输入工作频率,0 =一直输入SCLK频率,即使没有内存操作也会输入,1 =仅当进行内存数据操作时才输入SCLK频率,通常设置为1

lBK76MAP:设置Bank6/7的内存容量,笔者使用开发板内存为两片32M内存芯片并联成64M,它们全部都外接到Bank6上,因此选择0b001

lBANKSIZE寄存器设置为:0xb1

(6)SDRAM模式设置寄存器MRSRx (SDRAM MODE REGISTER SET REGISTER)

表2-22 SDRAM模式设置寄存器(MRSRx)

该寄存器用于设置CAS潜伏周期,可以手动设置的位只有CL[6:4]位,通过前面内存工作原理可知,笔者使用开发板CL=3,即0b011

lMRSR6,MRSR7设置为:0x00000030

1.1.8内存驱动实验

设置该工程加载时运行时地址为0x30000000,如图2-55所示:图2-55设置加载时运行时地址

init.s:本程序文件主要实现了,关闭看门狗,初始化内存,拷贝ROM数据到内存中,然后跳往内存中执行xmain函数,从xmain函数返回之后,将全部

S3C2440SDRAM内存驱 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)