ARM汇编必知必会

ADC 带进位的32位数加法

ADD 32位数相加

AND 32位数的逻辑与

B 在32M空间内的相对跳转指令

BIC 32位数的逻辑位清零

BKPT 断点指令

BL 带链接的相对跳转指令

BLX 带链接的切换跳转

BX 切换跳转

CDP\CDP2 协处理器数据处理操作

CLZ 零计数

CMN 比较两个数的相反数

CMP 32位数比较

EOR 32位逻辑异或

LDC\LDC2 从协处理器取一个或多个32位值

LDM 从内存送多个32位字到ARM寄存器

LDR 从虚拟地址取一个单个的32位值

MCR\MCR2\MCRR 从寄存器送数据到协处理器

MLA 32位乘累加

MOV 传送一个32位数到寄存器

MRC\MRC2\MRRC 从协处理器传送数据到寄存器

MRS 把状态寄存器的值送到通用寄存器

MSR 把通用寄存器的值传送到状态寄存器

MUL 32位乘

MVN 把一个32位数的逻辑“非”送到寄存器

ORR 32位逻辑或

PLD 预装载提示指令

QADD 有符号32位饱和加

QDADD 有符号双32位饱和加

QSUB 有符号32位饱和减

QDSUB 有符号双32位饱和减

RSB 逆向32位减法

RSC 带进位的逆向32法减法

SBC 带进位的32位减法

SMLAxy 有符号乘累加(16位*16位)+32位=32位

SMLAL 64位有符号乘累加((32位*32位)+64位=64位)

SMALxy 64位有符号乘累加((32位*32位)+64位=64位)

SMLAWy 32位有号乘累加((32位*16位)>>16位)+32位=32位

SMULL 64位有符号乘累加(32位*32位)=64位

SMULxy 32位有符号乘(16位*16位=32位)

SMULWy 32位有符号乘(32位*16位>>16位=32位)

STC\STC2 从协处理器中把一个或多个32位值存到内存

STM 把多个32位的寄存器值存放到内存

STR 把寄存器的值存到一个内存的虚地址内间

SUB 32位减法

SWI 软中断

SWP 把一个字或者一个字节和一个寄存器值交换

TEQ 等值测试

TST 位测试

UMLAL 64位无符号乘累加((32位*32位)+64位=64位)

UMULL 64位无符号乘累加(32位*32位)=64位

基于RISC 的ARM CPU

ARM是一种RISC体系结构的处理器芯片。和传统的CISC体系结构不同,RISC 有以下的几个特点:

◆ 简洁的指令集——为了保证CPU可以在高时钟频率下单周期执行指令,RISC指令集只提供很有限的操作(例如add,sub,mul等),而复杂的操作都需要由这些简单的指令来组合进行模拟。并且,每一条指令不仅执行时间固定,其指令长度也是固定的,这样,在译码阶段就可以对下一条指令进行预取。

◆ Load-Store 结构——这个应该是RISC 设计中比较有特点的一部分。在RISC 中,CPU并不会对内存中的数据进行操作,所有的计算都要求在寄存器中完成。而寄存器和内存的通信则由单独的指令来完成。而在CSIC中,CPU是可以直接对内存进行操作的,这也是一个比较特别的地方。

◆ 更多的寄存器——和CISC 相比,基于RISC的处理器有更多的通用寄存器可以使用,且每个寄存器都可以进行数据存储或者寻址。

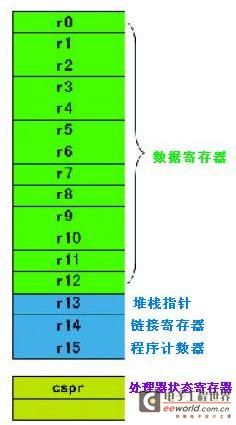

图:user模式下ARM处理器体系结构

◆ r13 - 指向当前栈顶,相当于x86的esp,这个东西在汇编指令中要用sp 表示

◆ r14 - 称作链接寄存器,指向函数的返回地址。用lr表示,这和x86将返回地址保存在栈中是不同的

◆ r15 - 类似于x86的eip,其值等于当前正在执行的指令的地址+8(因为在取址和执行之间多了一个译码的阶段),这个用pc表示

ARM 指令集

ARM处理器可以支持3种指令集——ARM,Thumb和Jazelle。

采用那种指令集,由cspr中的标志位来决定。大体说来:

◆ ARM——这是ARM自身的32 位指令集

◆ Thumb ——这是一个全16 位的指令集,在16 位外部数据

ARM汇 相关文章:

- STM32 arm汇编(thumb-2指令集)启动代码分析(12-02)

- ARM汇编程序基本知识(11-28)

- ARM汇编中伪指令的介绍(11-28)

- ARM汇编伪指令介绍(11-28)

- ARM汇编指令的一些总结(11-28)

- 常用ARM汇编指令(11-28)