AVR单片机(学习ing)-ATMEGA16的定时/计数器

四—(01)、四位显示秒表试验

首先怀念一下咱们的体育课,再体育课或者田径比赛的时候,老师会经常使用秒表来记录同学们的成绩。在此,来进行一个秒表的设计。( 说实话,这个秒表真的太贵了,不过只是实验,纯属娱乐)

说实话,这个秒表真的太贵了,不过只是实验,纯属娱乐)

使用INT0键进行计时的开始/停止,使用S1键作为计时值得清楚,并且采用6位数码管的右四位进行显示。

定时器T0被用作扫描4位数码管(采用溢出中断,每1ms中断一次),而定时器T1则用来计时(咱们用的秒表用来显示四位,两位小数,也就是每计时10ms中断溢出一次)。

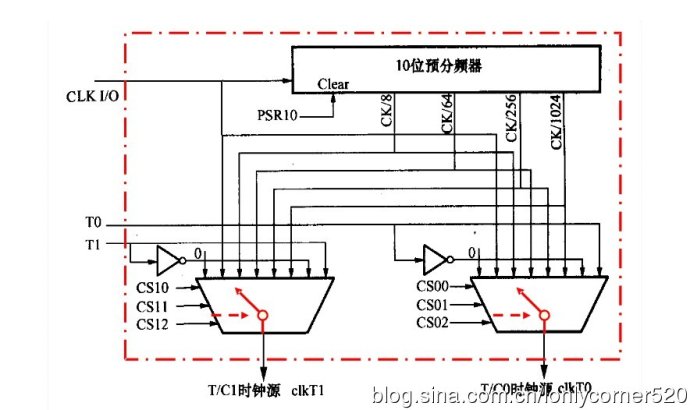

1、预分频器和多路选择器

ATMEGA16有两个8位定时/计数器(T/C0、T/C2)和一个16位定时/计数器(T/C1)。

ATMEGA16的定时器/计数器时钟是可选择的。其时钟部分包括预分频器和一个多路选择器。预分频器课被认为是一个有多级输出的分频器。ATMEGA16用一个10位的计数器把输入的时钟分为4种可选择的分频输出。多路选择器可设置使用其中一个分频输出,或者不适用分频输出和使用外部引脚输入时钟。

看图看真相:(其中只有0和1的,2的同理啊~好像那个0和1共用一个,具体我给忘记了,自己看datasheet~)

2、8 位定时器/ 计时器0

T/C0 是一个通用的单通道8 位定时器/ 计数器模块。其主要特点如下:

• 单通道计数器

• 比较匹配发生时清除定时器( 自动加载)

• 无干扰脉冲,相位正确的PWM

• 频率发生器

• 外部事件计数器

• 10 位的时钟预分频器

• 溢出和比较匹配中断源 (TOV0 和 OCF0)

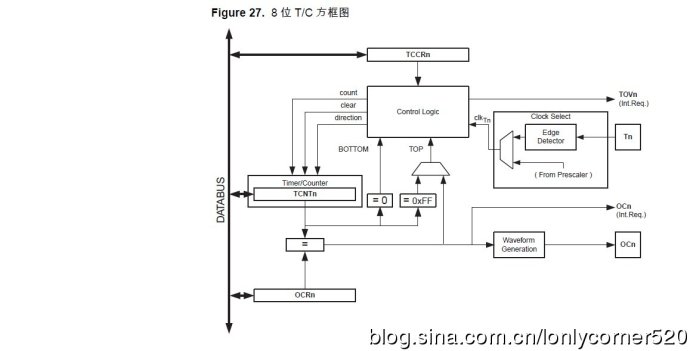

Figure 27为8位定时器/计数器的简化框图(说实话,我也看不懂啊~~ )

)

寄存器:

T/C(TCNT0)和输出比较寄存器(OCR0)为8位寄存器。中断请求(图中简写为Int.Req. ) 信

号在定时器中断标志寄存器TIFR 都有反映。 所有中断都可以通过定时器中断屏蔽寄存器

TIMSK 单独进行屏蔽。图中没有给出TIFR 和TIMSK。

T/C可以通过预分频器由内部时钟源驱动,或者是通过T0 引脚的外部时钟源来驱动。时钟

选择逻辑模块控制使用哪一个时钟源与什么边沿来增加( 或降低)T/C 的数值。如果没有

选择时钟源T/C 就不工作。时钟选择模块的输出定义为定时器时钟clkT0。

双缓冲的输出比较寄存器OCR0 一直与T/C 的数值进行比较。比较的结果可用来产生

PWM波,或在输出比较引脚OC0上产生变化频率的输出。比较匹配事件还将置位比较标志OCF0。此标志可以用来产生输出比较中断请求。

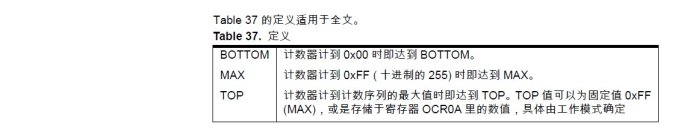

定义:

本文的许多寄存器及其各个位以通用的格式表示。小写的“n” 取代了T/C 的序号,在此即

为0。小写的“x” 取代了输出比较单元通道,在此即为通道A。但是在写程序时要使用精

确的格式,例如使用TCNT0 来访问T/C0 计数器值,等等。

T/C 时钟源:

T/C 可以由内部同步时钟或外部异步时钟驱动。时钟源是由时钟选择逻辑决定的,而时钟

选择逻辑是由位于T/C 控制寄存器TCCR0 的时钟选择位CS02:0 控制的。

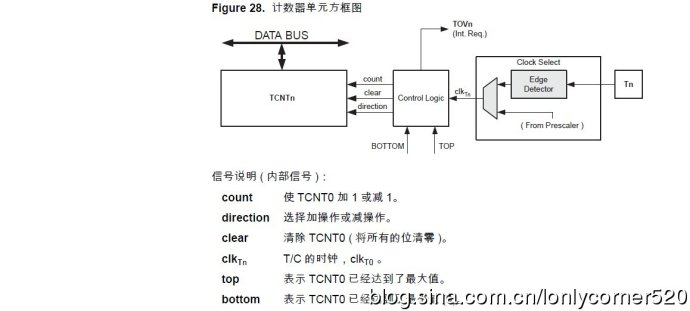

计数器单元:

8位T/C的主要部分为可编程的双向计数单元。 Figure 28 即为计数器和周边电路的框图。

根据不同的工作模式,计数器针对每一个clkT0 实现清零、加一或减一操作。clkT0 可以由

内部时钟源或外部时钟源产生,具体由时钟选择位CS02:0 确定。没有选择时钟源时

(CS02:0 = 0) 定时器即停止。但是不管有没有clkT0,CPU 都可以访问TCNT0。CPU 写操

作比计数器其他操作( 如清零、加减操作) 的优先级高。

计数序列由T/C 控制寄存器 (TCCR0) 的WGM01 和WGM00 决定。计数器计数行为与输

出比较OC0 的波形有紧密的关系。有关计数序列和波形产生的详细信息请参考P72“ 工作

模式” 。

T/C溢出中断标志TOV0根据WGM01:0 设定的工作模式来设置。TOV0可以用于产生CPU

中断。

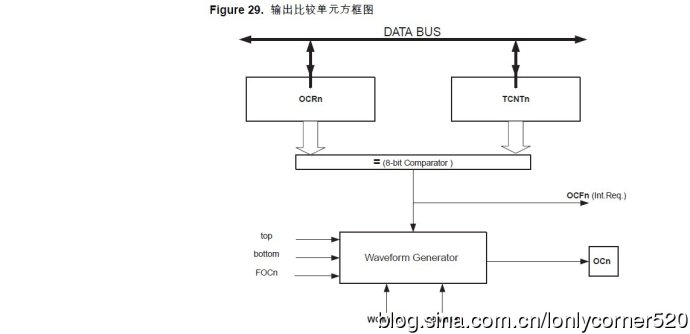

输出比较单元:

8位比较器持续对TCNT0和输出比较寄存器OCR0进行比较。一旦TCNT0等于OCR0,比

较器就给出匹配信号。在匹配发生的下一个定时器时钟周期输出比较标志OCF0 置位。若

此时OCIE0 = 1 且SREG 的全局中断标志I 置位,CPU 将产生输出比较中断。执行中断

服务程序时OCF0 自动清零,或者通过软件写”1” 的方式来清零。根据由WGM21:0 和COM01:0 设定的不同的工作模式,波形发生器利用匹配信号产生不同的波形。同时,波

形发生器还利用max 和bottom 信号来处理极值条件下的特殊情况

Figure 29 为输出比较单元的方框图。

使用PWM 模式时OCR0 寄存器为双缓冲寄存器;而在正常工作模式和匹配时清零模式

双缓冲功能是禁止的。双缓冲可以将更新OCR0 寄存器与top 或bottom 时刻同步起来,

从而防止产生不对称的PWM 脉冲,消除了干扰脉冲。

访问OCR0 寄存器看起来很复杂,其实不然。使能双缓冲功能时,CPU 访问的是OCR0

缓冲寄存器;禁止双缓冲功能时CPU 访问的则是OCR0 本身。(好了,你笨上就这么多吧,我还是看书上的排版比较好啊~~datasheet真的好大啊~``)

AVR单片机ATMEGA16定时计数 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)