一种智能ARI NC429总线接口板的硬件设计与实现

随着航空电子系统综合性的增强,各个系统之间的数据通讯,变得尤为重要。ARINCA29作为最常用的通讯总线,广泛使用在波音系列飞机、欧洲空中客车等机种,成为机载设备之间通讯的主要接口。我国的惯导系统,也以ARINc429为主要通讯总线。ANINC 429数字信息传输规范(D玎s)33为在航空电子设备之间传输数字信息,制定了航空运输工业标准。

ANINC 429的发送速度有高速(100 kbps)和低速(12.5 kbps)两种。对于低速发送,一般的嵌入式处理器(如8051系列单片机)即可满足;而对于高速发送,虽然采用性能更好的80C196单片机可以满足,但其外围电路繁冗,会影响板卡的性能。

同上述两种单片机相比,TMS320F206采用了先进的改进型哈佛结构及流水线技术,指令执行速度快。1个机器周期仅为50鹏。同时TMS320F206的数据、地址总线(均为16位)分开,片内带有32k字的闪速存储器和544个字的RAM。构成最小系统时非常简单,不需EPROM、RAM、地址数据锁存器。虽然用其构成ANINC 429数据传输系统时的指令同80C2196类似,但由于每条指令的执行时间很短,至少为80C196的1/20。故可使速度提高20多倍。从而不但可以满足高速ANINC 429数据传输的要求,而且能够减化板卡设计,提高板卡的性能。

1 HS3282芯片简介

HS3282是HARRIS公司推出的一款高性能的COMS型429总线接口电路,其工作频率为100 k bit或者12.5 k bit,单电源+5V供电,低功耗,直接与ARINC总线连接,一路发送,两路接收。接收器和发送器相互独立,同时工作。双通道接收器之间也是独立的并行接收,可以直接连接到APdNCA29总线。而不需电平转换。字长25位或者32位,接收数据时进行校验,而发送数据时产生校验,内部定时器可自动调整字间隙。其发送缓冲是一个8 X 32 Bit的FIFO。

2 总体设计

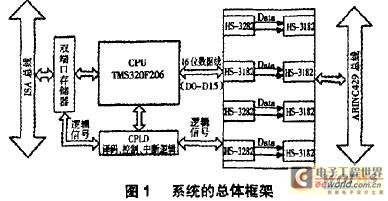

429总线接121板的主要功能,是在429总线和PC机之间起到桥粱作用,实现429总线数据信息的接收和发送。当有数据从429总线上传输时,429接口电路能够准确地将其接收,并把它送到DSP,经DSP处理后,继续向Pc机发送;当Pc机的信号传输到来时,由DSP进行实时处理后,控制429收发模块将数据传送到429总线上。系统的总体框架如图1所示。

图中,主要设计模块有以下部分:

(1)板卡CPU。选用TI公司的TMS320F206。是设计成本最低、结构功能复杂度也较低的定点DSP。其片内32kFlash、4.5kRAM可以满足处理规模适中的应用。可省去片外固化存储器,简化接口电路设计。但TMS320F206的I/O引脚数只有4个,远不能满足设计需要,因此还需要选用CPLD作为接口的扩展,并完成译码和部分控制工作。

(2)429总线接口电路。HS3282是ARINC429的协议芯片,发送时,常配合HS3182共同作为一组ARINC 429总线的接口电路。本板卡具有4发8收的功能,根据上述介绍,这里须要选用4组这样的总线接口电路。

(3)数据缓冲器。为避免PC机从双口存储器中读取数据时,DSP再次对该数据区进行写操作而产生冲突,选用双端口RAM连接ISA总线和DSP处理器。

(4)译码、控制和中断逻辑。这里采用CPLD来实现。因为CPLD具有编程方便、集成度高、速度快、价格低等特点,而且CPLD软件包中有各种输入工具、仿真工具、版图设计工具和编程器等全线产品,使设计人员在很短时间内,就可以完成电路的输入、编译、优化、仿真,直至芯片的制作。

3 CPLD模块的设计

3.1中断逻辑模块

429接口从外部接收到数据时,采用中断方式向F206发出请求,F206接到中断请求后,进人中断服务子程序。F206在处理完接收数据及对相应的状态进行设置后。向Pc机发出中断请求信号。PC机接收到中断请求信号后,通过查询各个状态字来获得接收口的通道号和数据量等信息,区分不同的中断源,若为接收中断,则首先通过查询缓冲状态位来判断接收通道,在将数据取走后,将此缓冲区的状态位清零。PC机每隔一段时间,将要发送的数据(若有数据)送到相应得缓冲区中,并以中断的方式通知429板,F206接收到中断请求后,将中断请求清除,再将数据取走并通知接口板进行发送。

(1)F206向Pc机发送中断的逻辑模块。图2中,中断拨码器的输出XIRQ的8个引脚分别与ISA总线的3,4,5,7,10,11,12,15这8个中断引脚相连,通过拨码,可以选择这8个中的—个。当F206要向PC机发送中断时,通过A1一A5将中断入口地址写到中断寄存器中,并通过CPLD的译码逻辑模块产生一个向Pc机的中断请求INTPC,INTPC经过中断寄存器产生INTRPC信号并通过拨码器SW产生—个中断信号XMQX(3,4,5,7,10,11,12,15中的—个),发往PC机。PC机接到F206发来的中断后,产生一个中断应答信号CLRINT

ARINC429总线DSPCPL 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)