高速差分线的PCB设计与仿真

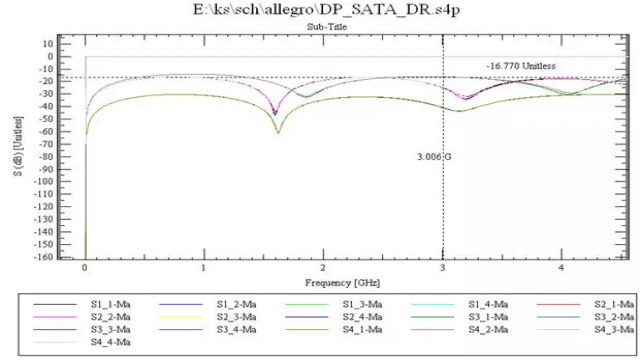

和后仿真,在利用allegro进行PCB设计的时候还需要结合仿真的结果实时的对设计进行修改以达到符合要求的目的。由于仿真过程复杂,步骤繁琐,在此不一一进行描述, 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,等长是为了保证两个差分信号时刻保持相反极性,减少共模分量。另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以前者side-by-side 实现的方式较多。等距则主要是为了保证两者差分阻抗一致,减少反射。对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值, 此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性(signal integrity)及时间延迟(timing delay)。从仿真的S参数曲线图可以分析差分对的差分阻抗(differential impedance),以及信号完整性。下面给出本设计中的关键信号仿真波形以供加以说明。 从仿真图例图5看到,S11在0-3.0GHz 的频域范围内其最劣化的指标为:-16.770db以下 ,S22(粉红色的曲线)也不劣于-17db。 这说明该差分对的差分阻抗(differential impedance)接近设计指标,信号完整性得到了保证。

图5:差分对线仿真S参数曲线

图6:差分对IN,OUT的HSPICE仿真图

通过差分对IN,OUT的HSPICE仿真,图6显示的结果:差分对线的对称良好。

结论 通过以上的仿真分析可知,在PCB的设计阶段对于高速LVDS信号的各项要求都能达到,而经过实际的PCB生产也证明了该设计的正确性,该产品运行稳定,完全能达到PCI-express高速数据传输的要求,可靠性高。由 本文的分析可知,在高速串行信号的设计中,不仅考虑电路设计,其板图设计和仿真分析也同样的重要,而且随着信号的频率越来越大,影响信号的延时、串扰、信 号完整性等的因素越来越复杂。同时控制这些因素的影响也越来越困难,工程师必须深入的分析布线设计、借助精确的模型、有效的仿真和科学的分析方法,才能给 复杂的高速设计以正确的指导,减少修正周期确保设计成功

- USB 3.0信号完整性测试简介(12-27)

- 针对0.4毫米和0.5毫米晶圆级封装的PCB设计(07-28)

- 射频电路的PCB设计(12-04)

- 电子元件面对高功率电平(01-04)

- 射频板材选材和无源互调(01-05)

- AWR和Zuken发布PCB射频验证流程(01-30)