技术分析:用于电机控制的Σ-Δ转换方案

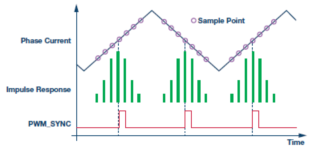

这可以通过对齐PWM_SYNC脉冲的脉冲响应中心轴来实现,如图5所示。

图5. 对齐sinc滤波器对PWM的脉冲响应

为了正确对齐PWM脉冲响应,必须知道脉冲响应的长度。 三阶滤波器的脉冲响应中的轴数为:

N × DR – 2

利用此式可以算出以秒为单位的脉冲响应长度:

tM (N × DR – 2)

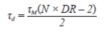

其中,tM为调制器时钟周期。 该时间值很重要,因为它告诉我们一个样本完全通过滤波器需要多长时间。 脉冲响应的中心轴恰好位于总滤波器长度的一半处,因此,一个样本走完一半路程所需的时间必定为:

所以,如果输入采样开始于PWM_SYNC之前的τd,并且在PWM_SYNC之后的τd读取滤波器数据,则对齐就会如图5所示。 采样开始由调制器时钟的使能/禁用来控制。 一旦使能,滤波器就会与PWM保持同步,无需再对齐。

控制时序

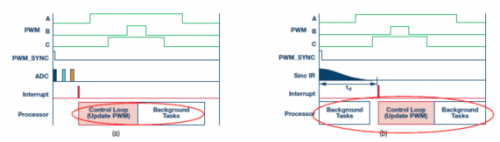

通过对齐PWM_SYNC脉冲响应,便可测量相电流而不会有混叠,但在读取滤波器数据时必须十分小心。 sinc滤波器在PWM_SYNC之前的τd启动,但数据需要2 × τd的时间才能通过滤波器。 换言之,必须在PWM_SYNC之后等待τd时间才能从滤波器读取数据。 只有在此刻,电流的真实平均值才可用。 与基于SAR的电流测量相比,这种方法在控制时序方面不相同,如图6所示。

在SAR情形(a)中,PWM_SYNC脉冲触发ADC执行若干采样和转换。 当数据对控制环路而言已就绪时,系统产生一个中断,控制环路便可开始执行。 而在Σ-Δ情形中,不是等待ADC,而是要让数据完全通过sinc滤波器。 当数据就绪时,系统产生一个中断,指示控制环路可以执行。 如果进行类比的话,SAR ADC的转换时间相当于脉冲响应时间的一半。 脉冲响应一半的具体长度取决于调制时钟和抽取率。 对于fM = 20 MHz且DR = 100的典型配置,脉冲响应的一半为τd = 7.4 μs。 虽然比快速SAR ADC略长,但数值差别不大。

图6. 控制算法时序,(a)使用SAR ADC,(b)使用Σ-Δ ADC.

图7. PI控制器方案。 (a)常规方案,(b) P路径和I路径分离,(c) P路径和I路径分离且反馈分离。

应当注意,在典型控制系统中,PWM定时器的零阶保持效应远远超过脉冲响应的一半,因此sinc滤波器不会严重影响环路时序。

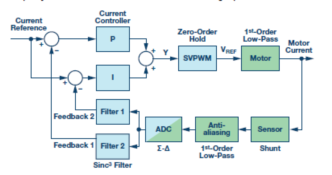

Σ-Δ ADC对控制性能的影响

采用Σ-Δ ADC,用户可以自由选择sinc滤波器延迟或输出数据保真度。 抽取率较高时,延迟较长,但信号质量较高; 抽取率较低时则相反。 这种灵活性对于电机控制算法设计十分有利。 通常,算法的某些部分对延迟敏感,而对反馈精度较不敏感。 其它部分适合在较低动态特性和较高精度下工作,但对延迟较不敏感。 举个例子,考虑图7 (a)所示的常规比例积分控制器(PI)4, 5。P部分和I部分采用相同的反馈信号工作,意味着该信号的动态特性必须适合两种控制路径。 不过,P路径和I路径可以分离,如图7 (b)所示。由此还可以再前进一小步,图7 (c)显示P路径和I路径分离,并且采用具有不同动态特性的反馈信号工作。

P部分的任务是抑制快速负载变化和快速速度变化,但精度不是主要考虑。 换言之,低抽取率和短延迟的sinc滤波器对P部分有利。 I部分的任务是确保稳态性能稳定且精确,它要求高精度。 因此,高抽取率和较长延迟的sinc滤波器对I部分有利。 这就产生了图8所示的实现方案。

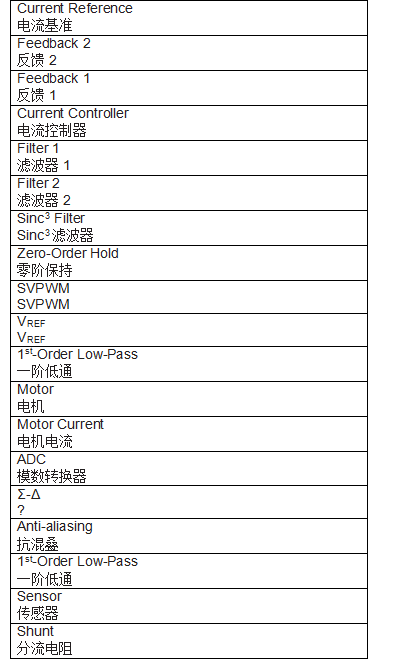

电机相电流由一个传感器(分流电阻)测量,并流经一个抗混叠滤波器,供应给Σ-Δ ADC。 然后,1位数据流输入两个sinc滤波器,一个针对P控制器调谐,另一个针对I控制器调谐。 为简明起见,图8省去了Clark和Park变换。 然而,电流控制是在一个旋转dq框架中完成。

图8. 双sinc滤波器和分离的电流控制器P路径和I路径

为了评估电流反馈分为两条路径的影响,我们对该闭环执行了稳定性分析。 对于传统的Z域分析,sinc滤波器会带来问题。 它会引入一个延迟,对于任何实际抽取率,该延迟小于一个采样周期。 例如,若系统以fsw = 10 kHz的速率运行,滤波器延迟将短于100 μs。 从控制环路方面看,sinc模块是一个小数延迟滤波器。 为了模拟小数延迟,将sinc滤波器近似看作一个全通滤波器。 在最高为奈奎斯特频率一半的较低频率时,该近似处理是精确的,但在更高的频率,其与理想滤波器有一些偏差。 然而,这里的目的是了解双反馈如何影响环路稳定性,就此而言,该近似是合适的。

作为对比,图9 (a)显示了反馈路径(无双反馈)中仅使用一个sinc滤波器时的闭环幅度响应。 开关频率fsw为10 kHz,奈奎斯特频率设置为5 kHz。 在这些系统参数下,对于0 μs至80 μs的sinc滤波器群延迟,绘

Σ-Δ转换SINC滤波器电机控 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)