电机驱动控制系统设计

1 IR21844主要特点及技术参数

IR21844集成驱动芯片与目前应用的集成驱动芯片相比,具有以下特点:

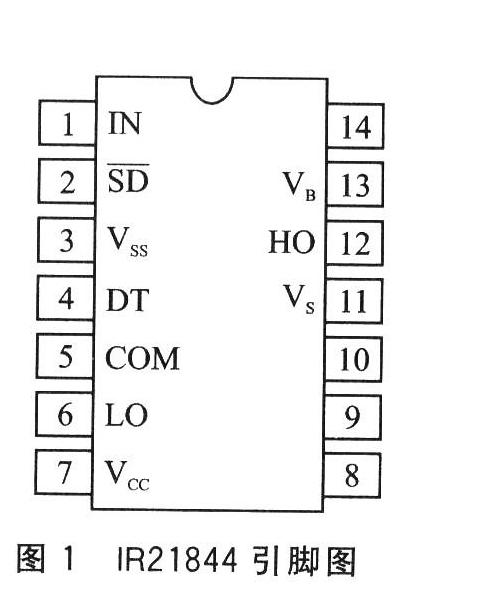

· 该芯片为标准14引脚单片式结构,图1为其引脚分布图;

· 设有悬浮截获电源可自举运行,其高端工作电压最高达600 V,抗du/dt干扰能力为50 V/ns,15 V时静态功耗为1.6 W;

· 输出栅极驱动电压范围较宽,为10~20 V;

· IR21844采用CMOS工艺制作,逻辑电路和功率电路共用一个电源,电压范围为10~20 V,适应TTL或CMOS逻辑信号输入;

· 采用CMOS施密特触发输入,以提高电路抗干扰能力;

· 具有独立的高端和低端2个输出通道,两路通道均带有滞后欠压锁定功能;

· 容许逻辑电路参考地(VSS)与功率电路参考地(COM)之间有一5~+5 V的偏移量;

· 死区时间可调。

图1中,引脚1(IN)是逻辑输入控制端;引脚6和12是2路独立的输出,分别是L0(低端输出)和H0(高端输出);引脚7和13分别是VCC(低端电源电压)和VB(高端浮置电源电压);引脚5(COM)是低端电源公共端;引脚11和3分别是VS(高端浮置电源公共端)和VSS(逻辑电路接地端);引脚2(SD)是输出关闭控制端;引脚4(DT)是可调的死区时间输入端。

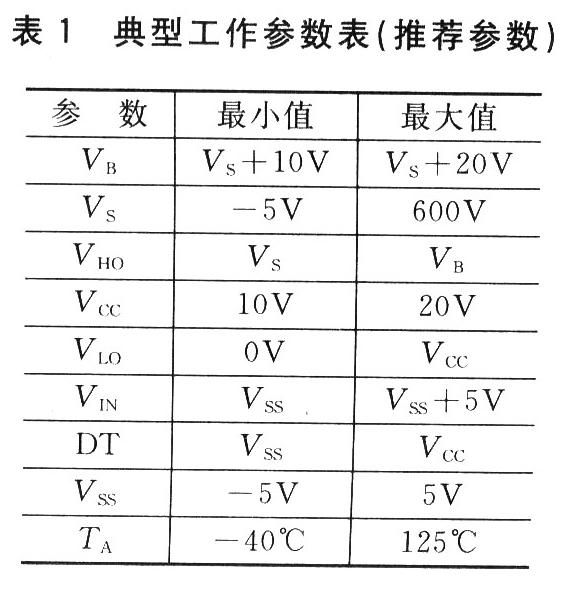

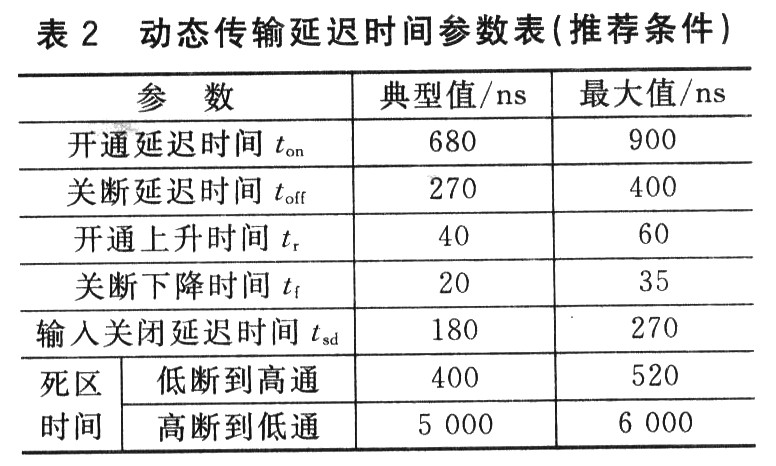

其推荐典型工作参数如表1所列,动态传输延迟时间参数如表2所列。

2 典型应用电路

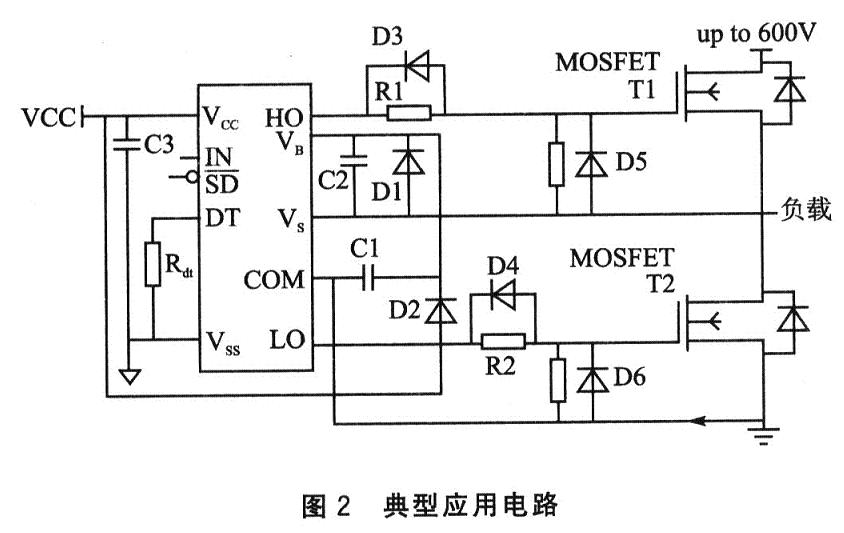

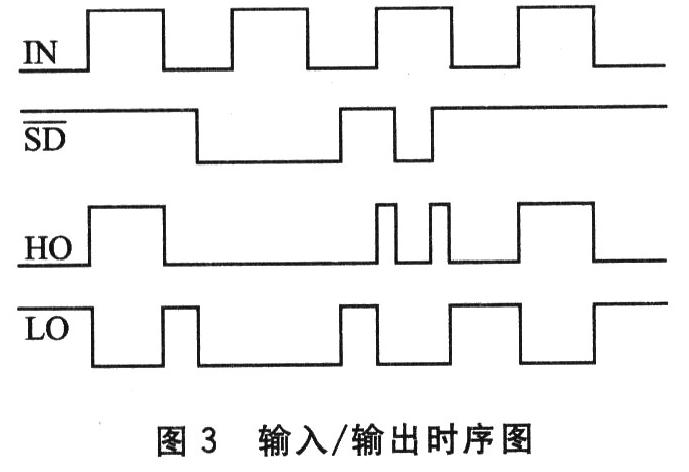

图2为IR21844的典型应用电路。Vcc接电源端,为逻辑部件和功率器件供电;IN端接输入控制信号,一般接PWM信号;输出端HO和LO的波形分别与IN端输入波形逻辑相同和相反,幅值有一定的放大(10~20 V),输入/输出时序图如图3所示;SD端接低电平时,H0和LO正常输出,接高电平时,2个输出端被封锁;DT为死区时间调整端,因为桥式电路同一桥路的上下管不能同时导通,否则会造成管子短路,因此需要一个死区时间。由于H0和LO的输出逻辑相反,所以从逻辑上来说,不会造成直通,但是在换向的瞬间仍有可能造成直通。可在DT端外接一个电阻Rdt,通过调整该电阻的阻值就可以调节死区时间;同时,开通延时时间为680 ns,大于关断延时时间的270 ns,从而避免桥路的直通,死区时间典型值为5μs(如表2所列)。

图2中,C2为自举电容。在T2导通、T1关断期间,VCC经D1、C1、负载、T2给C1充电,以确保当T2关断、T1导通时,T1管的栅极靠Cl上足够的储能来驱动。这就是高端的自举供电。若负载阻抗较大,C2经负载降压充电较慢,使得T2关断、T1导通,C2上的电压仍充电不到自举电压8.3 V以上,那么输出驱动信号会因欠压被片内逻辑封锁,T1就无法正常工作。为此,C2的选择就显得很重要,一般用1个大电容和1个小电容并联使用,在频率为20 kHz左右的工作状态下,选用1.0μF和0.1μF电容并联。并联高频小电容用来吸收高频毛刺干扰电压。驱动大容量的IGBT时,在工作频率较低的情况下,要注意自举电容电压稳定性问题,上管的驱动波形峰顶如果出现下降的现象,则要选取大的电容。

显然每个周期T1开关一次,C2就通过T2开关充电一次,因此自举电容C2的充电还与输入信号IN的PWM脉冲频率和脉冲宽度有关。当PWM工作频率过低时,若T1导通脉宽较窄,自举电压8.3 V容易满足;反之,无法实现自举。因此,要合理设置PWM开关频率和占空比调节范围,C2的容量选择考虑如下几点:

①PWM开关频率高,C2应选小电容。

②尽量使自举上电回路不经大阻抗负载,否则应为C2充电提供快速充电通路。

③对于占空比调节较大的场合,特别是在高占空比时,T2导通时间较短,C2应选小电容。否则,在有限时间内无法达到自举电压。

④C2的选择应综合考虑PWM变化的

电机驱动控制系 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)