2.5 GS/s高速DAC的陶瓷外壳设计

匹配验证

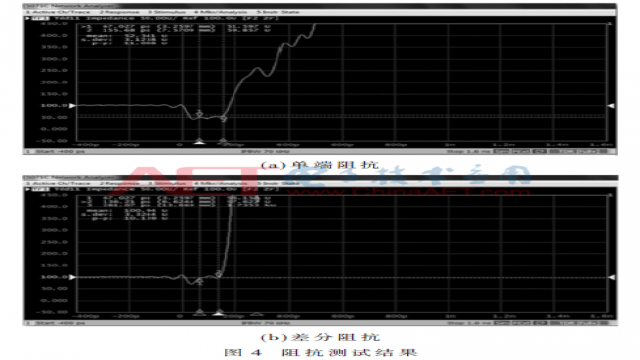

为了评估本次设计中阻抗匹配的情况,使用矢量网络分析仪对外壳中关键时钟信号差分对和高速数字输入信号差分对进行了差分阻抗和单端阻抗测试。图4分别为时钟信号差分对的单端阻抗和差分阻抗的测试结果。从图4可以看出,单端阻抗在50 Ω±10%范围,差分阻抗在100 Ω±10%范围,满足了产品对阻抗匹配的设计要求。

2.1.2 传输损耗分析

为了评估外壳中走线的传输性能,使用Sigrity对高速信号差分对进行了S参数提取,图5为高速时钟信号差分对的插入损耗的提取结果。可以看出在信号的最高频率2.5 GHz以内,插入损耗保持在-0.8 dB以内,满足了差分时钟信号的传输要求。另外,由于陶瓷外壳多层电源/地平面的影响,相邻层中的电源/地平面相当于一个谐振腔,其传输特性曲线在4.1 GHz处会出现了谐振现象,本设计通过对电源/地的设计将谐振频点控制在信号的工作频率之外。

2.1.3 电源性能分析

要评价电源分布系统的电性能,通常通过电源地网络的环路电感和电容、宽带短路阻抗进行评价。本文以最相邻的地平面为参考平面,对每一个电源网络进行环路电感和电容提取,结果如表2所示,可以看出电源网络的环路电感都在1 nH以下,电源的供电稳定性得以保障。

另外,提取了4个电源网络的宽带短路阻抗曲线,如图6所示,可以看到该封装的第一谐振、第二谐振分别可能出现在1.95 GHz和2.67 GHz处,可以通过后期在PCB上加电容将谐振频点调整到芯片的工作频带之外。

2.2 芯片、封装、PCB的协同设计与优化

使用Sigrity对从芯片bump到PCB上信号输入端的整个传输路径进行传输特性分析,进行整个系统的协同设计与仿真。本设计在空间允许的情况下,通过改变PCB上走线拖布,有效地降低了信号的传输损耗,提升了整个传输路径的传输性能。图7所示为原设计和优化布线后的S参数结果。图8所示为在PCB上添加去耦电容前后的目标阻抗变化情况。可以看出,通过添加去耦电容,有效地降低了供电系统VDD的电源地阻抗,提高了供电系统的稳定性。

3 结论

本文完成了一款高可靠14 bit 2.5 GS/s高速数模转换器芯片的陶瓷外壳设计,介绍了电学设计的流程,阻抗测试结果表明外壳的阻抗匹配情况满足了设计要求,同时外壳关键信号路径的传输性能可以保证高速信号的可靠传输,以及关键传输路径的传输性能;另外,通过芯片、封装与PCB的协同仿真优化,有效地降低了整个系统传输路径的损耗,提升了电源系统工作的稳定性。在以后的高速电路封装与系统设计中,应充分利用协同设计来提升整个系统的性能。

参考文献

[1] Thomas Whipple.IC-package co-design and analysis for 3D-IC designs[C].IEEE,2009.

[2] Krishna Bharath.Signal and power integrity co-simulation for multi-layered system on package modules[C].IEEE,2007.

[3] Xavier Lecoq.Challenges in IC-package-PCB co-design of an advanced Flip-Chip PoP package for a mobile application[C].EMPC,2013.

[4] YANG L.Power integrity characterization and correlation of 3D package systems using on-chip measurements[C].Proc.of IEEE EPEPS,2010:221-224.

[5] Krishna Bharath.Signal and power integrity co-simulation for multi-layered system on package modules[C].IEEE,2007.

- 基站射频卡时钟树设计问题(05-03)

- 理解和设计高速D/A转换器的宽带输出网络(01-12)

- DAC和ADC助力射频通信(02-11)

- 信号完整性相关问题分析(09-23)

- 使用TDR、网分和建模技术获得信号完整性的技巧(11-25)

- 信号完整性和电磁兼容的一些问题的分析(01-20)