2.5 GS/s高速DAC的陶瓷外壳设计

引言

随着集成电路向低电压、大电流、高密度、高速度方向发展,工作电压的降低使所容许的噪声容限越来越小,集成密度的增加使得串扰越来越大,过高的工作频率带来反射、色散等传输线效应,信号失真、时序错误给信号传输带来了很大的挑战。集成电路封装作为连接芯片与系统的桥梁,高速电路的封装设计在很大程度上决定了电子系统的性能指标,封装设计过程中的信号完整性分析已经成为系统设计中重要的研究内容。

一个完整的高速系统设计涵盖了芯片设计、封装设计和PCB设计。随着信号频率的提高,系统越来越复杂,线性设计流程很难甚至难以达到系统性能的设计要求,同时芯片、封装、PCB都不能孤立存在,它们是相互作用、相互影响的。芯片-封装-PCB的协同设计能够综合考虑系统性能的要求,它在设计之初就要对系统的设计余量有一个通盘的考虑,发现整个设计过程中的设计瓶颈,合理分配设计余量,可以有效提高设计效率。本文旨在使用协同设计来实现军用高可靠陶瓷封装的设计以及系统性能的优化。针对采样速率为2.5 GS/s的高速数模转换器,完成了陶瓷外壳的封装设计,并利用协同设计完成了对系统性能的优化设计。

1 设计实现

1.1 设计分析

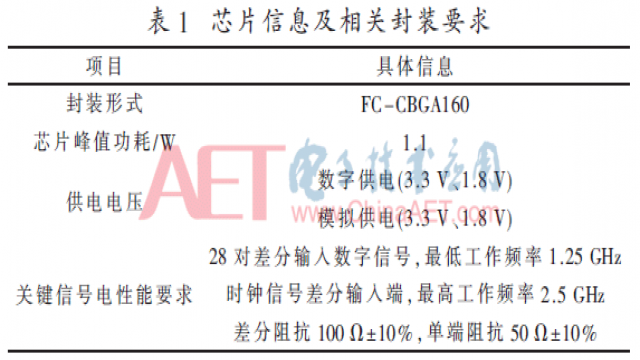

封装设计的目的是为芯片提供合适的封装解决方案,需要对研发成本、开发时间以及封装的性能进行严格的设计折中。而对于高速集成电路的封装,由于互连传输结构具有了高频传输线的特性,产品性能成为各种设计折中最主要的矛盾。协同设计方法能够综合考虑芯片、封装及PCB之间的互相影响,可以减少设计过程的迭代,降低设计成本,缩短产品上市时间,有效解决产品性能与研发成本及产品上市时间之间的矛盾。本文中芯片引出端信息及相关要求如表1所示。

从本产品性能的角度分析,封装设计要做到如下几点:(1)阻抗匹配,尽量保证整个传输路径的阻抗连续性,减小信号的反射;(2)由于输入并行信号的要求,信号线要等长;(3)要对4个供电电源的分布进行设计,以保证电源供电的稳定性;(4)为了保证设计的一次成功性,需要使用协同设计和系统仿真进行设计的验证与优化。

1.2 结构设计

封装结构设计是进行集成电路陶瓷封装设计的起点,芯片封装形式的确认是一款产品封装设计的第一步。如果用户有具体的封装要求,要先评估其合理性,然后确定封装形式及封装结构;如果没有特定的封装要求,要先根据芯片的I/O数目和关键信号的频率以及电源、地的数目,进行封装形式的选择和评估。

按照产品需求,本产品封装形式为FC-CBGA,根据芯片尺寸、外壳生产厂家的工艺规则、封装工艺要求及相关外壳设计规范,确定该产品的互连结构示意图如图1所示。结合产品高可靠性的要求,采用某陶瓷外壳公司的氧化铝陶瓷基板,基板尺寸为12×12 mm2,按照用户要求,采用气密性封装,密封盖板为可伐合金盖板。

1.3 阻抗匹配及层叠设计

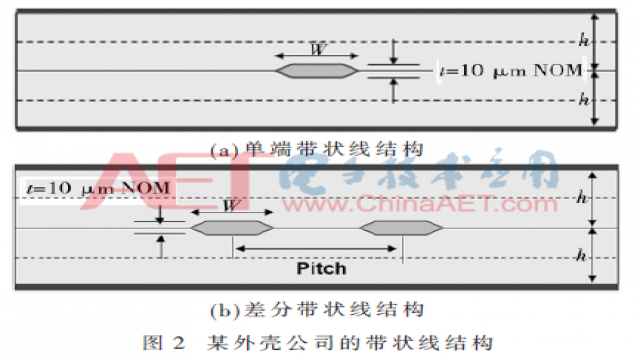

信号传输路径的阻抗匹配是封装设计中非常关键的一步,良好的阻抗匹配能够有效地降低信号的反射,降低传输路径的损耗,保证信号的可靠传输。封装陶瓷基板中单端带状线和差分带状线的结构如图2所示。这种结构可增强信号线的抗干扰能力,若信号线为干扰源,也可以降低该干扰源对其他信号的影响。为了满足产品对阻抗匹配的要求,分别对单端阻抗和差分阻抗进行了设计,结合层叠结构和介质材料的电学参数,确定单端线的线宽为75 μm,差分线的线宽为65 μm,线间距为240 μm,氧化铝介质层厚度为200 μm。

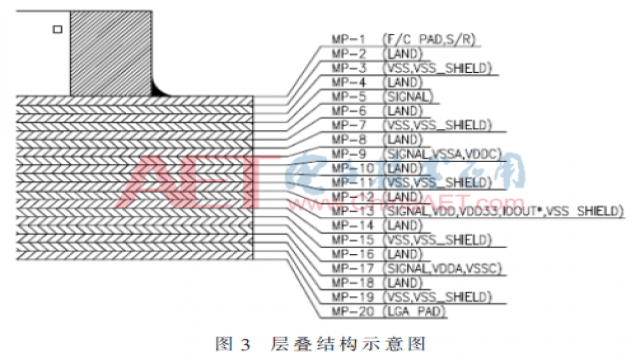

合理的叠层设计对于高速信号的可靠传输而言是至关重要的,它不仅有利于信号线布线,还可以非常有效地减少串扰及为信号提供返回路径,而且能够减小电源网络的输入阻抗及电源噪声。另外,合理的封装叠层设计能够使电源、地平面的谐振频率落在系统的工作频率之外,同时能够减少电磁辐射。本文通过信号和电源、地之间的协同规划,得出了符合设计要求和信号完整性要求的叠层设计方案:整个陶瓷基板分为11层,Top层为倒装焊焊盘,Bottom层为BGA焊盘,另外有4个信号层,信号层都被参考平面层包围,具体的叠层分布情况如图3所示。

2 测试分析与验证优化

使用传统的测试方法来得到封装的电气特性,耗费时间和成本,如果运用软件快速的评估封装的电性能,将大大提高封装在高速应用领域的可靠性。本文使用Sigrity进行陶瓷外壳的电学性能分析,并通过芯片-封装-PCB的协同设计与仿真,完成了对整个系统传输性能和电源系统稳定性的提高。

2.1 封装电性能分析

2.1.1 阻抗

- 基站射频卡时钟树设计问题(05-03)

- 理解和设计高速D/A转换器的宽带输出网络(01-12)

- DAC和ADC助力射频通信(02-11)

- 信号完整性相关问题分析(09-23)

- 使用TDR、网分和建模技术获得信号完整性的技巧(11-25)

- 信号完整性和电磁兼容的一些问题的分析(01-20)