基于ADS和Matlab的超宽带低噪声放大器的频带选择性设计

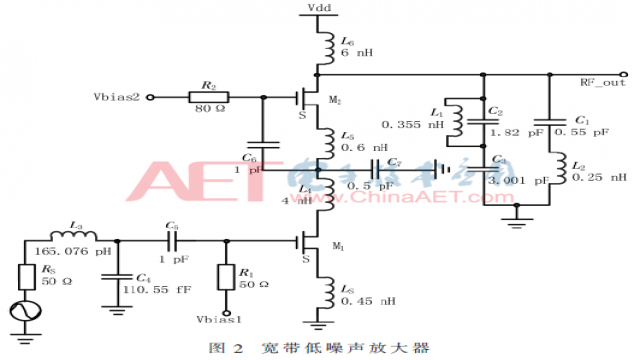

路中的输入回路中的电容恰好形成谐振,可实现输入阻抗匹配。由于两个晶体管M1和M2在同一条偏置电路上,电流的功耗即为原来的一半,因为高频信号首先全部从晶体管M1的栅极流入,从晶体管M1的漏极流出时分为两路,一路经过电容C6再流入晶体管M2,再最终从晶体管M2的漏极流出,另外一路高频信号经过电感L4和电容C7到地。

2 仿真结果分析

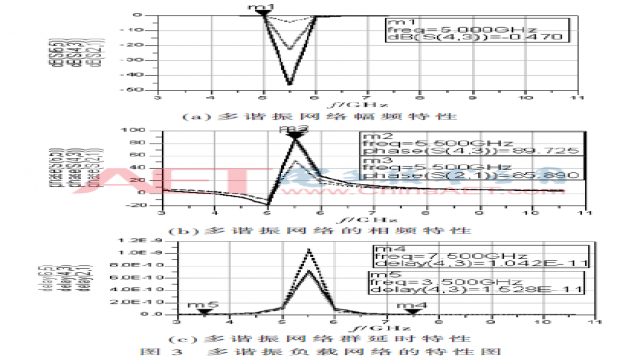

基于ADS仿真平台,将多谐振网络搭载到ADS软件下,调用S参数仿真器,在超宽频段内对幅频、相频以及网络特性上作出仿真,结果如图3所示。点线代表图1(a)提出的电路结构,长虚线表示图1(b)电路结构,长实线表示图1(c)电路结构。图3(a)展示出本文提出的多谐振网络的优势,干扰信号的衰减性强,上下边频拥有非常平坦的导通特性。图3(b)展示了多谐振网络的相位特性,本文提出的结构在WLAN信号的中心频率点5.5 GHz处的相频特性相差达到了89.725°,较之图1(a)和图1(b)多谐振网络能更好地使来自WLAN的干扰信号发生正交化,干扰信号就很容易被后续的相位鉴频器检查出来,从而更好地实现相频上的选择特性。图3(c)表现了多谐振网络的群延时特性,上下边频群延时都保持在同一数量级上,而在WLAN频带里则产生高量级的延迟,体现了频带选择网络对载波包络良好的选择性。

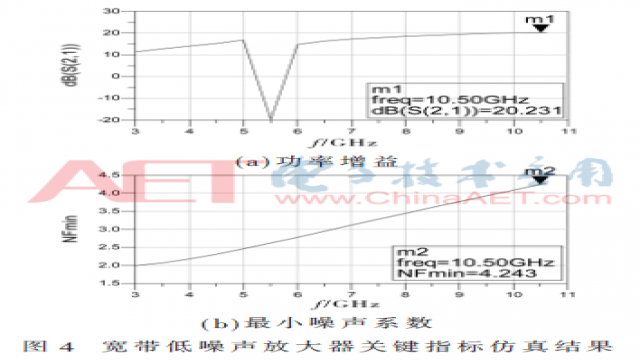

基于0.18 μm CMOS工艺利用ADS仿真软件对整个频带选择性的低噪声放大电路进行仿真,其结果如图4所示。其图4(a)显示了放大器的放大性能,也很好地反映出多谐振网络对无用信号的选频能力。上下通频带内,放大电路的增益超过10 dB,并对无用信号的幅度衰减也达到-20 dB。图4(b)为电路最小噪声系数随频率的变化关系,可以看出电路噪声性能良好,最小噪声系数小于4.25 dB。

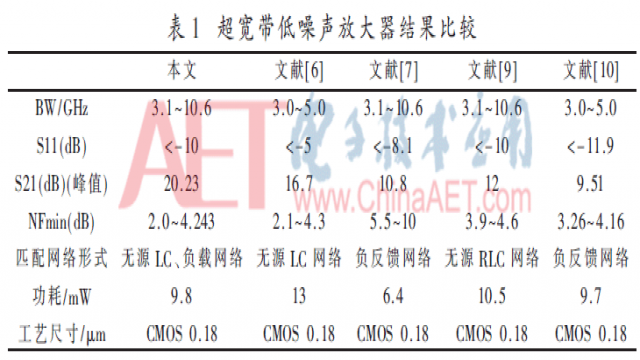

由表1中的参考数据可以说明:由于采用了无源LC输入匹配网络和电流复用结构,本电路的结构与参考文献相比较在其他性能参数略有缺憾的条件下具有工作带宽大、增益大、噪声较低、功耗较低的优点。

3 结论

本文论述了一种具有频带选择性的超宽带低噪声放大器的设计,提出新的多谐振负载选频网络以及引入电感源极负反馈的放大电路结构,最终使得放大电路在噪声和功率传输下都获得了良好的性能。仿真结果表明:在3.1 GHz~10.6 GHz频带内,稳定性良好,S11小于-10 dB,最大功率传输增益为20.23 dB,最小噪声系数在4.25 dB以下。同时与其他文献结果比较,该结构具有工作带宽大、功耗较低、面积省、增益大等优点,具有应用价值。

参考文献

[1] PARK B,LEE K,CHOI S,et al.A 3.1-10.6 GHz RF receiver front-end in 0.18 μm CMOS for ultra-wideband applications[J].IEEE MTT-S International Microwave Symposium digest.IEEE MTT-S International Microwave Symposium,2010:1616-1619.

[2] MIYAKE H,KITAZAWA S,ISHIZAKI T,et al.A miniaturized monolithic dual band filter using ceramic lamination technique for dual mode portable telephones[J].Journal of Bacteriology,1997,2(3):1333-44.

[3] PARK B H,JUNG J H.Design of a full-band CMOS UWB receiver and fast-hopping carrier generator for 3.1-10.6 GHz[J].Analog Integrated Circuits & Signal Processing,2014,79(1):45-56.

[4] PERUMANA B G,ZHAN J H C,TAYLOR S S,et al.Resistive-Feedback CMOS low-noise amplifiers for multiband applications[J].IEEE Transactions on Microwave Theory & Techniques,2008,56(5):1218-1225.

[5] CUSMAI G,BRANDOLINI M,ROSSI P,et al.A 0.18 μm CMOS selective receiver front-end for UWB applications[J].IEEE Journal of Solid-State Circuits,2006,41(8):1764-1771.

[6] ALAVI-RAD H,ZIABAKHSH S,ZIABAKHSH S,et al.A 0.9 V CMOS 3-5 GHz broadband flat gain low-noise amplifier for ultra-wide band receivers[J].Electrical & Computer Engineering Canadian Journal of,2013,36(2):87-91.

[7] HSU M T,HSIEH Y C,OU A C.Design of low power UWB CMOS LNA using RC feedback and body-bias technology[C].ASIC(ASICON),2013 IEEE 10th International Conference on.IEEE,2013:1-4.

[8] 赵常余.具有频带选择性的超宽带低噪声放大器的设计[D].绵阳:西南科技大学,2010.

[9] 华明清,王志功,李智群.0.18 μm CMOS 3.1~10.6 GHz超宽带低噪声放大器设计[J].电路与系统学报,2007,

- 220GHz无源三倍频器设计(11-04)

- 基于ADS软的卫星"动中通"微带双工器的设计(12-21)

- 一种低误码率的ADS-B接收机的设计(06-08)

- 基于CPLD的OMA-L137与ADS1178数据通信设计方案(09-11)

- m推演型声表面波高通滤波器设计(11-27)

- 基于P I N管的开关限幅器仿真与设计(05-17)