AXI总线学习

AXI 有读地址和控制、读数据、写地址和控制、写数据、写响应5个通道。

控制和数据通道分离,可以带来很多好处。地址和控制信息相对数据的相位独立,可以先发地址,然后再是数据,这样自然而然的支持显著操作,也就是outstanding操作。Master访问slave的时候,可以不等需要的操作完成,就发出下一个操作。这样,可以让slave在控制流的处理上流水起来,达到提速的作用。同时对于master,也许需要对不同的地址和slave就行访问,所以可以对不同的slave 连续操作。而这样的操作,由于slave返回数据的先后可能不按照master 发出控制的先后进行,导致出现了乱序操作(out of order )。

同时相对AHB 接口的单向hready信号,AXI的5个通道由双向的valid和ready信号进行握手。同时在读写操作中,有last 信号表明当前传输的是最后一个数据。

AXI的性能

AXI 能够使SoC 以更小的面积、更低的功耗,获得更加优异的性能。AXI获得如此优异性能的一个主要原因,就是它的单向通道体系结构。单向通道体系结构使得片上的信息流只以单方向传输,减少了延时。

选择采用何种总线,我们要评估到底怎样的总线频率才能满足我们的需求,而同时不会消耗过多的功耗和片上面积。ARM一直致力于以最低的成本和功耗追求更高的性能。这一努力已经通过连续一代又一代处理器内核的发布得到了实现,每一代新的处理器内核都会引入新的流水线设计、新的指令集以及新的高速缓存结构。这促成了众多创新移动产品的诞生,并且推动了ARM架构向性能、功耗以及成本之间的完美平衡发展。

AXI总线是一种多通道传输总线,将地址、读数据、写数据、握手信号在不同的通道中发送,不同的访问之间顺序可以打乱,用BUSID来表示各个访问的归属。主设备在没有得到返回数据的情况下可发出多个读写操作。读回的数据顺序可以被打乱,同时还支持非对齐数据访问。

AXI总线还定义了在进出低功耗节电模式前后的握手协议。规定如何通知进入低功耗模式,何时关断时钟,何时开启时钟,如何退出低功耗模式。这使得所有IP在进行功耗控制的设计时,有据可依,容易集成在统一的系统中。

AXI的特点

单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

增强的灵活性。AXI技术拥有对称的主从接口,无论在点对点或在多层系统中,都能十分方便地使用AXI技术。

AXI4的工作模式

握手机制

AXI4所采用的是一种READY,VALID握手通信机制,即主从模块进行数据通信前,新根据操作对各所用到的数据、地址通道进行握手。主要操作包括传输发送者A等到传输接受者B的READY信号后,A将数据与VALID信号同时发送给B。如下图所示:

axi总线的五个通道:

- 读地址通道,包含ARVALID, ARADDR, ARREADY信号;

- 写地址通道,包含AWVALID,AWADDR, AWREADY信号;

- 读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;

- 写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;

- 写应答通道,包含BVALID, BRESP, BREADY信号;

- 系统通道,包含:ACLK,ARESETN信号;

其中ACLK为axi总线时钟,ARESETN是axi总线复位信号,低电平有效;读写数据与读写地址类信号宽度都为32bit;READY与VALID是对应的通道握手信号;WSTRB信号为1的bit对应WDATA有效数据字节,WSTRB宽度是32bit/8=4bit;BRESP与RRESP分别为写回应信号,读回应信号,宽度都为2bit,‘h0代表成功,其他为错误。

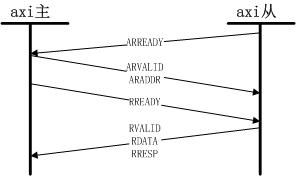

A.读操作:

顺序为主与从进行读地址通道握手并传输地址内容,然后在读数据通道握手并传输所读内容以及读取操作的回应,时钟上升沿有效。如图所示:

B.写操作:

顺序为主与从进

AXI总线学 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)