PCIe总线的基础知识

是一个相对的概念。如上图所示,Switch与EP2连接的PCIe链路,对于EP2而言是上游链路,而对Switch而言是下游链路。

在上图所示的Switch中含有3个端口,其中一个是上游端口(Upstream Port),而其他两个为下游端口(Downstream Port)。其中上游端口与RC或者其他Switch的下游端口相连,而下游端口与EP或者其他Switch的上游端口相连。

在Switch中,还有两个与端口相关的概念,分别是Egress端口和Ingress端口。这两个端口与通过Switch的数据流向有关。其中Egress端口指发送端口,即数据离开Switch使用的端口;Ingress端口指接收端口即数据进入Switch使用的端口。

Egress端口和Ingress端口与上下游端口没有对应关系。在Switch中,上下游端口可以作为Egress端口,也可以作为Ingress端口。如图4?5所示,RC对EP3的内部寄存器进行写操作时,Switch的上游端口为Ingress端口,而下游端口为Egress端口;当EP3对主存储器进行DMA写操作时,该Switch的上游端口为Egress端口,而下游端口为Ingress端口。

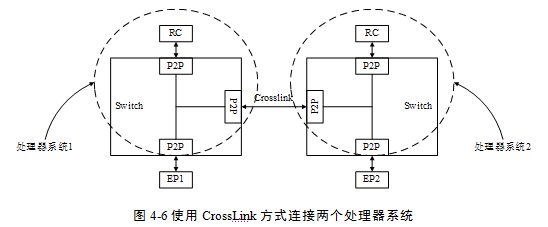

PCIe总线还规定了一种特殊的Switch连接方式,即Crosslink连接模式。支持这种模式的Switch,其上游端口可以与其他Switch的上游端口连接,其下游端口可以与其他Switch的下游端口连接。

PCIe总线提供CrossLink连接模式的主要目的是为了解决不同处理器系统之间的互连,如图4?6所示。使用CrossLink连接模式时,虽然从物理结构上看,一个Switch的上/下游端口与另一个Switch的上/下游端口直接相连,但是这个PCIe链路经过训练后,仍然是一个端口作为上游端口,而另一个作为下游端口。

处理器系统1与处理器系统2间的数据交换可以通过Crosslink进行。当处理器系统1(2)访问的PCI总线域的地址空间或者Requester ID不在处理器系统1(2)内时,这些数据将被Crosslink端口接收,并传递到对端处理器系统中。Crosslink对端接口的P2P桥将接收来自另一个处理器域的数据请求,并将其转换为本处理器域的数据请求。

使用Crosslink方式连接两个拓扑结构完全相同的处理器系统时,仍然有不足之处。假设图4?6中的处理器系统1和2的RC使用的ID号都为0,而主存储器都是从0x0000-0000开始编址时。当处理器1读取EP2的某段PCI总线空间时,EP2将使用ID路由方式,将完成报文传送给ID号为0的PCI设备,此时是处理器2的RC而不是处理器1的RC收到EP2的数据。因为处理器1和2的RC使用的ID号都为0,EP2不能区分这两个RC。

由上所述,使用Crosslink方式并不能完全解决两个处理器系统的互连问题,因此在有些Switch中支持非透明桥结构。这种结构与PCI总线非透明桥的实现机制类似,本章对此不做进一步说明。

使用非透明桥仅解决了两个处理器间数据通路问题,但是不便于NUMA结构对外部设备的统一管理。PCIe总线对此问题的最终解决方法是使用MR-IOV技术,该技术要求Switch具有多个上游端口分别与不同的RC互连。目前PLX公司已经可以提供具有多个上游端口的Switch,但是尚未实现MR-IOV技术涉及的一些与虚拟化相关的技术。

即便MR-IOV技术可以合理解决多个处理器间的数据访问和对PCIe设备的配置管理,使用PCIe总线进行两个或者多个处理器系统间的数据传递仍然是一个不小问题。因为PCIe总线的传送延时仍然是制约其在大规模处理器系统互连中应用的重要因素。

PCIe总线基础知 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)