PCIe总线的基础知识

e设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源Vcc。在PCIe总线中,WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。值得注意的是产生该信号的硬件逻辑必须使用辅助电源Vaux供电。

WAKE#是一个Open Drain信号,一个处理器的所有PCIe设备可以将WAKE#信号进行线与后,统一发送给处理器系统的电源控制器。当某个PCIe设备需要被唤醒时,该设备首先置WAKE#信号有效,然后在经过一段延时之后,处理器系统开始为该设备提供主电源Vcc,并使用PERST#信号对该设备进行复位操作。此时WAKE#信号需要始终保持为低,当主电源Vcc上电完成之后,PERST#信号也将置为无效并结束复位,WAKE#信号也将随之置为无效,结束整个唤醒过程。

PCIe设备除了可以使用WAKE#信号实现唤醒功能外,还可以使用Beacon信号实现唤醒功能。与WAKE#信号实现唤醒功能不同,Beacon使用In-band信号,即差分信号D+和D-实现唤醒功能。Beacon信号DC平衡,由一组通过D+和D-信号生成的脉冲信号组成。这些脉冲信号宽度的最小值为2ns,最大值为16us。当PCIe设备准备退出L2状态(该状态为PCIe设备使用的一种低功耗状态)时,可以使用Beacon信号,提交唤醒请求。

4SMCLK和SMDAT信号

SMCLK和SMDAT信号与x86处理器的SMBus(System Mangement Bus)相关。SMBus于1995年由Intel提出,SMBus由SMCLK和SMDAT信号组成。SMBus源于I2C总线,但是与I2C总线存在一些差异。

SMBus的最高总线频率为100KHz,而I2C总线可以支持400KHz和2MHz的总线频率。此外SMBus上的从设备具有超时功能,当从设备发现主设备发出的时钟信号保持低电平超过35ms时,将引发从设备的超时复位。在正常情况下,SMBus的主设备使用的总线频率最低为10KHz,以避免从设备在正常使用过程中出现超时。

在SMbus中,如果主设备需要复位从设备时,可以使用这种超时机制。而I2C总线只能使用硬件信号才能实现这种复位操作,在I2C总线中,如果从设备出现错误时,单纯通过主设备是无法复位从设备的。

SMBus还支持Alert Response机制。当从设备产生一个中断时,并不会立即清除该中断,直到主设备向0b0001100地址发出命令。

上文所述的SMBus和I2C总线的区别还是局限于物理层和链路层上,实际上SMBus还含有网络层。SMBus还在网络层上定义了11种总线协议,用来实现报文传递。

SMBus在x86处理器系统中得到了大规模普及,其主要作用是管理处理器系统的外部设备,并收集外设的运行信息,特别是一些与智能电源管理相关的信息。PCI和PCIe插槽也为SMBus预留了接口,以便于PCI/PCIe设备与处理器系统进行交互。

在Linux系统中,SMBus得到了广泛的应用,ACPI也为SMBus定义了一系列命令,用于智能电池、电池充电器与处理器系统之间的通信。在Windows操作系统中,有关外部设备的描述信息,也是通过SMBus获得的。

5JTAG信号

JTAG(Joint Test Action Group)是一种国际标准测试协议,与IEEE 1149.1兼容,主要用于芯片内部测试。目前绝大多数器件都支持JTAG测试标准。JTAG信号由TRST#、TCK、TDI、TDO和TMS信号组成。其中TRST#为复位信号;TCK为时钟信号;TDI和TDO分别与数据输入和数据输出对应;而TMS信号为模式选择。

JTAG允许多个器件通过JTAG接口串联在一起,并形成一个JTAG链。目前FPGA和EPLD可以借用JTAG接口实现在线编程ISP(In-System Programming)功能。处理器也可以使用JTAG接口进行系统级调试工作,如设置断点、读取内部寄存器和存储器等一系列操作。除此之外JTAG接口也可用作“逆向工程”,分析一个产品的实现细节,因此在正式产品中,一般不保留JTAG接口。

6PRSNT1#和PRSNT2#信号

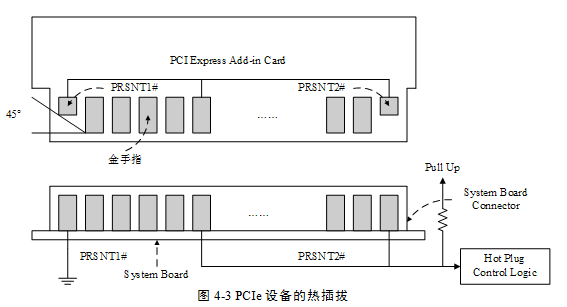

PRSNT1#和PRSNT2#信号与PCIe设备的热插拔相关。在基于PCIe总线的Add-in卡中,PRSNT1#和PRSNT2#信号直接相连,而在处理器主板中,PRSNT1#信号接地,而PRSNT2#信号通过上拉电阻接为高。PCIe设备的热插拔结构如图4?3所示。

如上图所示,当Add-In卡没有插入时,处理器主板的PRSNT2#信号由上拉电阻接为高,而当Add-In卡插入时主板的PRSNT2#信号将与PRSNT1#信号通过Add-In卡连通,此时PRSNT2#信号为低。处理器主板的热插拔控制逻辑将捕获这个“低电平”,得知Add-In卡已经插入,从而触发系统软件进行相应地处理。

Add-In卡拔出的工作机制与插入类似。当Add-in卡连接在处理器主板时,处理器主板的PRSNT2#信号为低,当Add-In卡拔出后,处理器主板的PRSNT2#信号为高。处理器主板的热插拔控制逻辑将捕获这个“高电平”,得知Add-In卡已经被拔出,从而触发系统软件

PCIe总线基础知 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)