高速便携式RS232/422信号模拟器设计

时间:12-16

来源:互联网

点击:

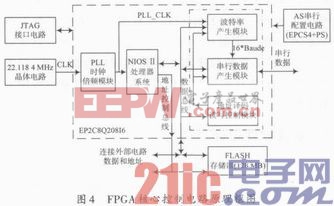

3.1 波特率和串行数据产生模块设计

串行数据产生模块负责生成符合格式设置要求的串行数据,如起始位,数据位,效验位,停止位等。它主要是把控制器发送的并行数据转换成串行数据,并根据控制器发送的效验位,停止位等设置命令来设置数据的格式,以来自波特率产生模块的16倍的波特率作为全局时钟,生成要模拟的RS232/422信号数据。

波特率产生模块根据控制器发送的命令数据来产生符合要求的波特率。在本系统中,要求产生24种标准和非标准的波特率,其中标准的波特率16种,非标准波特率8种,最高的波特率达到1 Mb/s,这样利用常规的分频器不能满足要求。

依据DDS(直接数字频率合成)的原理,结合积分分频电路,设计了频率字累加器,通过从NIOSⅡ控制器输入的频率字来控制累加器的累加步长,将累加器输出的最高位作为输出的时钟信号的方法实现所需要的波特率时钟,此时输出的时钟即可作为串行数据产生模块的全局时钟,也就是16倍的波特率。同时为了提高时钟的精确度,降低误码率,在系统时钟(这里采用的是22 11 8 4 MHz)进入分频器以前,利用PLL倍频电路提高时钟的频率。

波特率和串行数据产生模块在FPGA内部的原理实现框图如5图所示。它的实现是采用VHDL硬件描述语言实现的,框图中每个小的模块代表VHDL语言编制的模块程序。

3.2 NIOSⅡ控制器系统定制和内部程序设计

传统的MCU,DSP或ARM等硬处理器或控制器,它们的功能和片内外设都是固化好的,用户只能使用,而不能做任何改动。而NIOSⅡ处理器是FPGA芯片生成厂商Altera公司无偿提供的软IP核,可以通过QuanusⅡ软件对它进行设置,随时可以添加在片的ROM或RAM,并去掉不必要的外设,使得整个系统的搭建灵活,方便,简洁。并且,在硬件系统的设计上,一片FPGA芯片内就可以完成整个的数字控制系统,使得硬件系统的设计非常的简单可靠,性能也非常的稳定。

在本系统的设计中,NIOSⅡ处理器和传统的MCU,DSP或ARM等硬处理器或控制器一样,也可以用C语言编程实现需要的控制功能,也可以嵌入各种嵌入式操作系统,并进行调试等。编程的开发环境是专用的NIOS2-IDE集成开发环境。

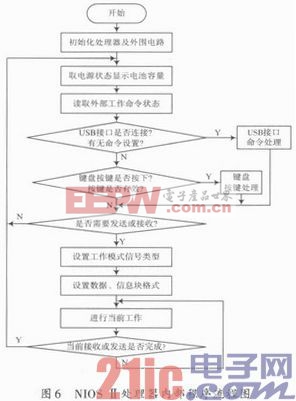

NIOSⅡ处理器内部程序主要完成USB与PC机之间的通信协议,依据PC机发送的设置命令来完成具体RS232/422信号的实现,并完成数据格式的设置,数据块的设置,数据下行发送和上行传输及信号源工作状态的显示。其内部程序流程图如图6所示。

3. 3 用户界面程序设计

信号仿真器在PC机端的软件设计包括设备驱动程序和用户程序两部分,FTDI公司为基于FT245RL的USB接口设备提供了VCP、D2XX(动态链接库)两种驱动程序,这样就不再需要自己设计设备驱动程序,而只需要选择不同的驱动程序,可以把主要精力投入在用户软件设计上面。

底层驱动程序主要完成上位计算机和硬件设备的连接功能,并为用户界面程序建立和信号源仿真器相互通信的通信协议和通道,其结构框图如图7所示。

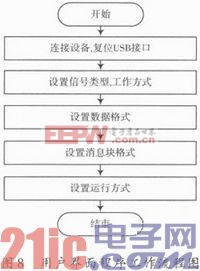

用户界面程序主要完成用户对模拟信号源进行的工作模式选择,信号种类选择,数据格式设置和消息块格式设置的输入功能,同时可以预览信号源发送的信号数据,读取信号源接收到的数据,并可以对存贮数据的FLASH芯片进行擦除。依据其要完成的功能,其流程图如图8所示。

本文研制的高速RS232/422信号仿真器,即可以由计算机通过USB接口控制使用,也可以依靠自身携带的电池、键盘和LED显示屏独立工作。它在设计中采用了FPGA技术,免除了程序跑飞的可能,提供了高速的,多种标准和非标准的波特率,灵活的数据格式和信息块格式设置,是机载测试采集器采集RS232/422信号进行实验室通电或外场排除RS 232/422总线数据故障时比较理想的选择。

高速便携式RS232422信号模拟 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)