高速便携式RS232/422信号模拟器设计

0 引言

随着我国航空技术的不断发展,我国新研制了众多不同型号和不同用途的飞机。这些飞机以及这些飞机上电子设备之间采用的RS 232和RS 422格式传输的数据总线也有了极大的发展。它们传输数据的数据位、校验位、停止位、波特率及传输的信息块形式各不相同,尤其波特率,已经从当初的几十Kb/s发展到现在的上百Kb/s甚至上Mb/s。这就需要研制一种高速RS 232/422信号模拟器,它能够模拟我国现有飞机及机上设备采用RS 232或RS 422格式进行相互通信的RS 232/422总线数据,为机载测试工程师在试验室对机上采集RS 232或RS 422信号的设备进行通电和编程验证,以及外场机上排故时提供方便可靠而又灵活的RS 232/422信号模拟器。

1 系统总体方案设计

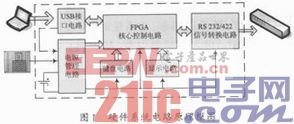

RS 232/422信号模拟器主要由USB接口、键盘显示、电源管理、RS 232/422信号电平转换和FPGA核心控制这几部分电路模块组成。USB接口电路主要功能是和上位计算机通过USB接口建立连接,把上位计算机发送数据传送到FPGA核心控制电路,或者把FPGA核心控制电路发送的数据传送到上位计算机。键盘显示电路主要功能是当信号模拟器脱离PC机独立工作时,通过键盘输入命令和数据,并在LED显示屏上观察输入的命令和数据是否正确,并可以在接收时能察看接收到的数据,以判断接收到的数据正确与否;此外,它还可以实时显示电源的状态和电池的电量等信息。电源管理主要是对供电源头进行排序和自动选择,同时监控电池的电量信息,并把这些信息传送给FPGA核心控制电路。

RS 232/422信号电平转换电路主要功能则是把TTL或CMOS电平转换成符合要求电平传送出去,或者把接收到的RS232或RS 422标准的信号电平转换成TTL或COMS电平,同时在不工作时使这些电路处于睡眠状态,以降低功耗。FPGA核心控制电路是本硬件系统的核心,它对以上部分的电路系统进行统一管理,监控所有电路的工作状态,并随接收来自这些电路的数据信息,根据这些信息做出不同的处理,如果需要的话,并把部分结果在LED显示屏或者上位计算机屏幕上显示出来,供操纵者参考。本信号仿真器的硬件系统电路原理框图如图1所示。

2.1 USB接口电路模块设计

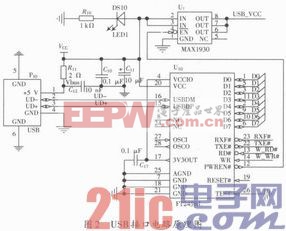

USB(Universal Serial Bus,(计算机)通用串行总线)是计算机和外围设备连接的最常用,也是最方便的总线接口,它支持热插拔和即插即用,应用灵活,易于升级,全速率传输可达12 Mb/s,而高速传输达480 Mb/s,并且它同时可以向外围设备提供耗电电流不大于500 mA的

5 V电源。在本信号仿真器中,USB接口不仅仅具有和信号仿真器交换数据的任务,同时还向信号源提供5 V的直流供电的功能。通过USB接口,上位计算机依靠用户界面程序对信号仿真器的工作状态、模拟的信号格式和信息块内容进行没置;当处于接收工作状态时,还可以把接收到的数据实时显示在计算机屏幕上。在设计中,本文采用了FTDI公司的FT245RL芯片作为主要的接口协议处理芯片,它本身集成了协议处理的固件程序,并且FTDI公司网站上也提供了此芯片的驱动程序,缩小了开发难度,加快了开发时间和成本。USB接口电路模块的电路原理图如图2所示。

信号模拟器既有USB接口供电,也有AC/DC适配器供电,同时还有着电池供电,这里供电电源的管理显得异常重要。在电源管理电路的设计中,首先要有电源排序和自动切换电路,当同时存在这三个电路供电时,要求能自动切断AC/DC和电池供电,无缝的转向USB供电。当USB接口不供电时,转向了AC/DC适配器供电,最后才是电池供电。整个过程的供电顺序是USB供电→AC/DC供电→电池;其次是要求能够对供电电路的状态和信息进行监控。电源管理电路模块要求能提供供电是来自USB接口、AC/DC适配器或是电池的信息,当是电池供电时,还需要提供电池的电量信息,即电池还剩余多少电量;最后,还要有锂离子充电电池的放电和充电的管理。为保护锂离子电池因过度放电而无法再次使用,当电池放电到终止电压时,自动切断供电电路,使电池供电电路处于断开状态。当插入AC/DC适配器和USB接口供电时,电源管理电路模块可以对电池进行充电,同时,电池的放电是一个电源逐渐衰减的过程,还需要对电源进行稳压。鉴于这些原因,电源管理电路模块的设计是本文的重难点之一。本系统中电源管理电路模块原理图如图3所示。

2. 3 FPGA核心控制电路模块设计

FPGA核心控制电路监控以上各电路模块的工作状态,随时准备接收来自它们的数据和命令,并进行相应的控制。它包括了控制部分和串行数据生成部分,控制部分是在FPGA芯片内部嵌入Alter公司提供的NIOSⅡ的处理器IP软核,利用QuartusⅡ软件内部的SOPC工具生成FPGA内部的控制电路。串行数据生成部分利用VHDL硬件编程语言编制了波特率发生器和并串转换模块生成RS232/422串行信号数据。所有的控制电路都是通过软件定制在一片FPGA芯片内,外围电路比较简单,除了正常的程序加载电路和程序存储芯片,仅需要一片时钟芯片即可。FPGA核心控制电路原理图如图4所示。

高速便携式RS232422信号模拟 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)